OPTION_5:HP

在电子产品中进行开关操作,直接或是间接雷击引起的瞬间过电压都会对设备产生干扰,而雷击涌浪测试就是用于来检验设备对于抵抗雷击涌浪的能力。根据IEC-61000-4-5所定出的雷击测试标准, 表一为对电源供应器所订定的规范。

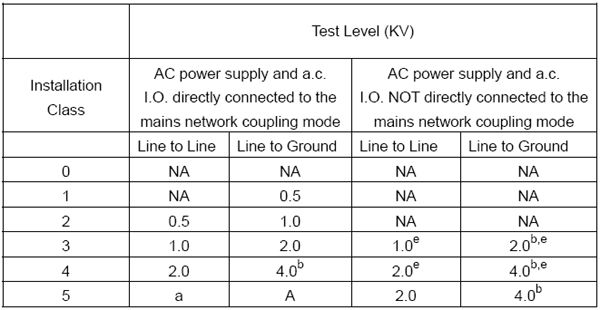

表一:Selection of the test levels

(Depending on the installation conditions)

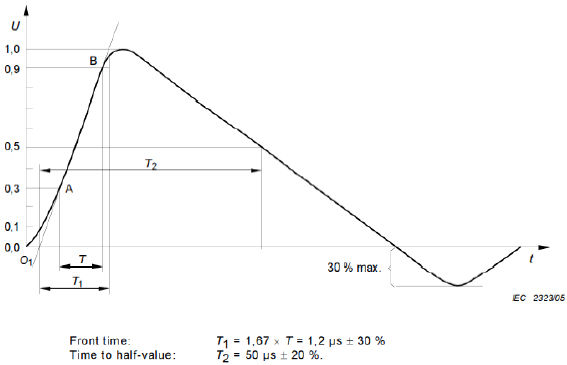

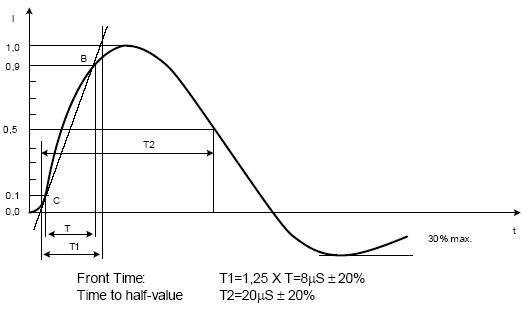

其雷击测试的波形有两种:Open Circuit Voltage Waveform 1.2m/50mS(图一)和Short Circuit Current Waveform 8/20mS (图二)。

图一:Open Circuit Voltage Waveform 1.2m/50mS

图二:Short Circuit Current Waveform 8/20mS

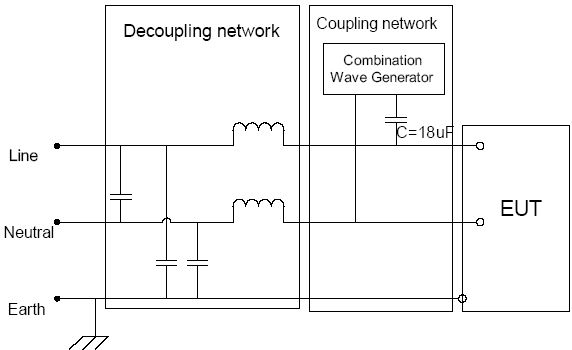

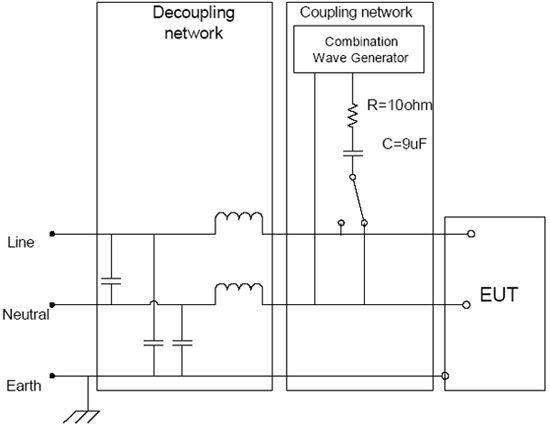

根据法规记载,其组合波信号产生器接线图如下图,电压会先经由Ccoupling(=18mF)进入Line或Neutral端。

图三:Single phase line to line Coupler/Decoupler Network

图四:Single phase line to earth Coupler/Decoupler Network

{pagination}

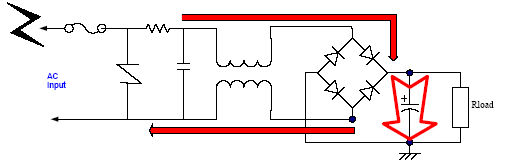

故在测试雷击测试时,无论Line对Neutral, Line或Neutral对Power Earth,雷击涌浪会依照下图所示路径,先经由MOV钳位后,再往大电容(C1)方面走,最后累积在大电容上,此时大电流会将大电容上的电压往上抬升至高电压,这高电压往往都会超过大电容的额定电压。

图五:雷击路径

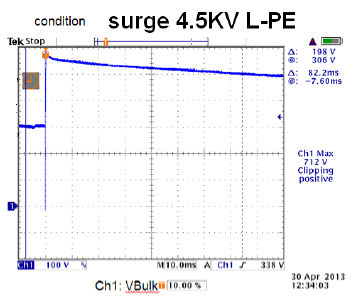

图六:大电容波形观察于雷击涌浪瞬间

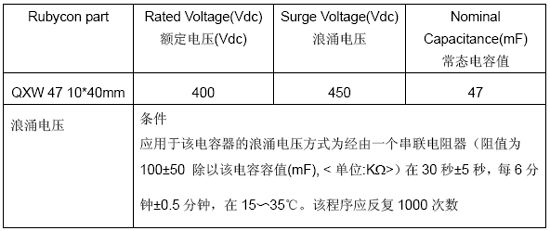

根据电容厂商的规格书记载,如下表二surge voltage测试。但这会因不同厂牌而有所不同。当雷击涌浪在大电容上产生的过高的电压(surge voltage),且累积次数过多,会有机会将电容里的电极铝箔损坏,小则大电容的顶部会突起,大则正负电极铝箔变形后正负短路而造成较大的损坏电流。如表二为例,400V额定电压的大电容,其可耐受的surge voltage为450Vdc (1000次)。

表二:大电容surge voltage耐受力定义(来源Rubycon corp.)

{pagination}

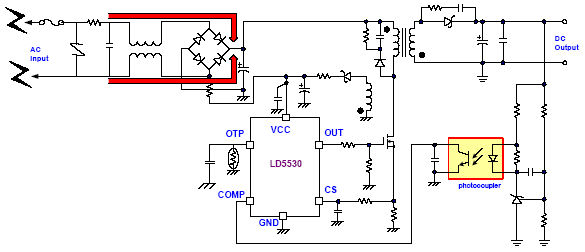

突然产生的损坏电流,会如下图七所示将所流经的零件瞬间烧毁。例如NTC, Fuse, L1(common choke)的铜线或绝缘漆,及桥式整流器的其中二颗整流二极管。

图七:雷击测试损坏路径

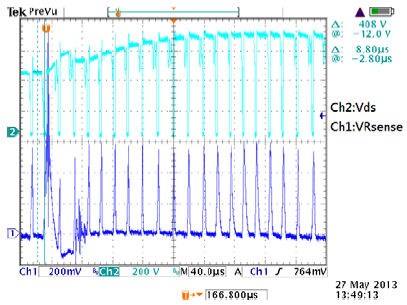

以实例24Watts(12伏特2安培)的范例中,测试电击电压4.5KV,所观测到的MOSFETVds电压如下图八。在雷击瞬间,Vds电压会因大电容电压被慢慢抬升而被垫高,此范例中的MOSFET为600伏特耐压,但图中的Vds压已被抬升至接近700伏特,此时MOSFET已进入Avalanch_breakdown(突崩溃:是指对半导体施加足够的电压时,流过它们的电流突然增大。强大的电流而产生的电子能够击出原子中的电子而使它变成自由电子。)。

图八:MOSFET与限流电阻之波形观察于雷击涌浪瞬间

{pagination}

一般来说共模电感的功用除了在EMI防制上的效果外,在雷击瞬间时,假设电感不饱和的情况下,雷击电压会被电感所抑制住,而产生出的雷击电流涌波也会比较低。但实际上共模电感会在发生电击瞬间后的几ms产生瞬间饱和现象,电感的阻抗瞬间消失,所有的电击电流涌波直接经由桥式整流器进入大电容。

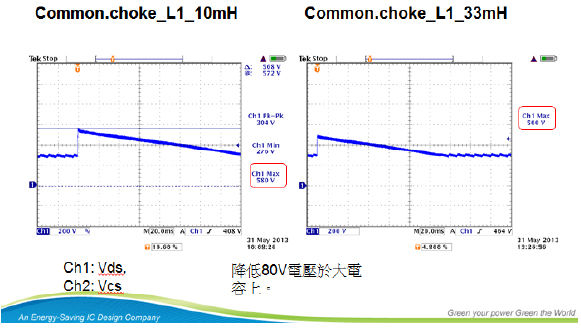

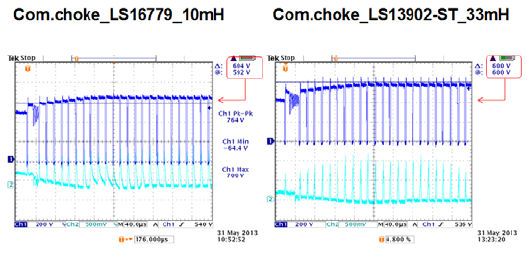

在实验中将共模电感的感量加大,来实测对大电容电压的影响。如图九所示,加大感量后,可以增加电感的感抗,并抑制雷击涌浪的能量,进而将大电容的电压压低,延长电容的使用寿命。并观察MOSFET的Vds耐压,也因此而降低不少,如图十。所以,防止共模电感在瞬间饱和的一般对策有加gas tube(气体放电管)、尖端放电layout等等。

图九:增大共模电感(1)

图十:增大共模电感(2)_ch1:Vds of MOSFET; ch2:VRsense

在雷击涌浪的防制中,除了Thermistor (NTC) , MOV(Metal Oxide Varistor ) , Gas Discharge Tube以外,共模电感也可以是其中一个防制组件,再搭配适当的安全距离设计,如变压器的绝缘距离,光耦合器的绝缘距离,Y电容的桥接地路径等,便可有效的强化对于抵抗雷击涌浪的能力。

{pagination}

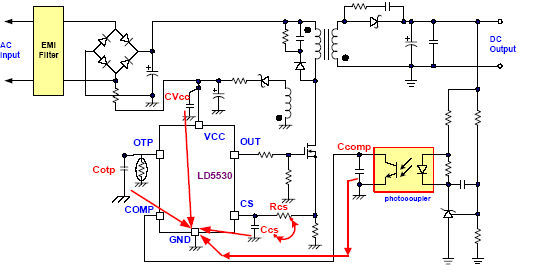

对于PWM IC部份,以通嘉(Leadtrend) LD5530 (SOT26)为例,如图十一所示。侦测Rsense的Rcs-Ccs filter需要尽量的靠近IC端,以防雷击瞬间产生的干扰。Ccomp电容和Cotp滤波电容也需靠近IC端以防干扰。而Vcc方面,由于LD5530有小于1uA的低激活电流与low power saving性能(no load<100mW@264VAC),其使用的Rstart_up可以相对较其它厂牌IC来的大,大的电阻(Rstart_up)对雷击瞬间产生的抵抗力也较强,可以抵抗较多的能量由激活电阻进入IC的Vcc pin,在PCB layout trace最后进入Vcc pin时,再加一个CVcc滤波电容0.1uF以稳定IC的Vcc OVP误动作是很重要的一个组件。对于某些6.6KV高雷击测试次数的规范来说,以上都可以有效强化电源产品的抵抗雷击涌浪的能力。

图十一:LD5530 PCB Layout建议

目前LD5530有低起动电流(1mA startup current)、低UVLO off电压(7.5V)及空载时低工作电流(0.65mA Operating current),对于在调整空载及轻载效能时有很大的助益,以65W为例, 264Vac输入条件时,空载损耗可以达到81mW以下,20W为例,空载损耗可以达到64mW以下。且具备有low cost design 与high performance的优势,内建Vcc OVP, SCP/OPP/OLP保护, 精准OCP high low line补偿,外部OTP保护与精准CS OVP设定之功能。