由英特尔(Intel)与美光(Micron)合资的IM Flash Technologies表示,该公司正计划为其NAND闪存芯片导入3D制程,目前正为这一开发制程寻找合适的新材料;此外,该公司也预计其20nm的2D存储器单元可望再微缩一、两代。

在日前举行的IMEC技术论坛上,英特尔公司技术与制造副总裁兼IM Flash公司执行长Keyvan Esfarjani证实了IM Flash公司正为开发3D NAND寻找新材料,同时也透露了开发策略的部份想法。

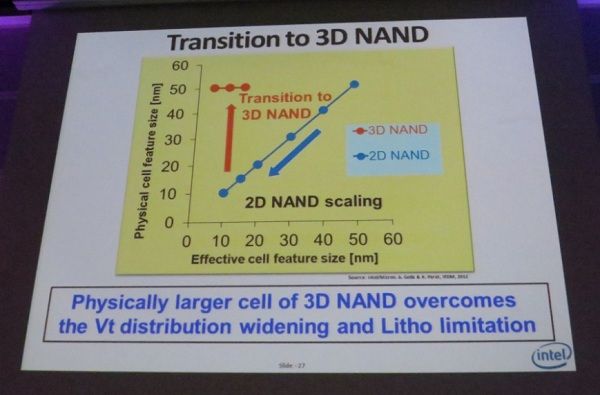

目前整个业界都预期非挥发性NAND闪存技术将将从2D存储器阵列过渡至NAND晶体管整合单芯片。3D存储器预计将以垂直半导体通道的方式排列,以多层环绕式栅极(GAA)结构形成多电栅级存储器单元晶体管。

东芝公司(Toshiba)率先以其p-BiCS技术导入3D NAND制程。该公司在去年底宣布开发出基于50nm直径垂直通道的16层元件。该元件预计在今年出样,2015年量产。东芝的p-BiC技术采用U形排列晶体管。

但Esfarjani指出, 2D NAND闪存存在微缩瓶颈,预计还可再微缩两代──在15nm与10nm节点。而第一个3D NAND可能出现在15nm 2D制程节点。Esfarjani并强调,16层NAND闪存芯片将不再符合经济效益,“你需要64或至少32层的NAND闪存。”

2D NAND闪存预计还可再微缩两代──15nm与10nm节点。

下一页:目前所面临的挑战在于测量 3D NAND将跨越10nm的限制

{pagination}

Esfarjani表示,IM Flash在20nm节点导入取代34nm与25nm“环绕式”单元的平面浮栅的高-K金属栅极单元,未来还可望再进一步微缩。IM Falsh公司在2012年利用其于逻辑电路取得的HKMG经验导入了128Gbit NAND闪存。

用于扩展2D NAND闪存的技术添加了氮化物薄膜与纳米点,Esfarjani指出,“但是可运作的单元还不够,你还需要达到10^5或更高周期的耐久性。”

“过渡到3D并不会受到微影技术的限制,”Esfarjani指出,直径40nm的半导体通道最适用。然而,目前业界所面临的挑战在于测量,以及找到一种最佳的材料──它必须能够承受多层半导体制程的温度以及高深宽比的蚀刻,才能驱动半导体内部垂直通道。而这必须精确地控制在89.8的锥度。

“再过几年将可实现这一NAND市场,同时它也将持续几年的成长。2D NAND持续采用平面浮栅单元,而3D NAND则将带领我们跨越10nm的限制。”Esfarjani总结道。

Esfarjani证实IM Flash正致力于为此3D NAND制程开发新材料,但并未透露细节。

Esfarjani表示IM Flash正为3D NAND开发新材料。

翻译:Susan Hong

本文授权翻译自EE TIMES,谢绝转载