2012年初,富士通半导体宣布交付其为中小型IC设计公司量身定制的55nm创新工艺制程(可兼容65nm IP、性能堪比40nm工艺),一度引发中国IC设计业的震动。而在日前于重庆举办的“中国集成电路设计业2012年会暨重庆集成电路跨越发展高峰论坛”上,富士通半导体又一次带来惊喜,率先将已经量产的成熟28nm先进工艺和设计服务带给中国高端SoC设计业者。

图1:富士通在重庆ICCAD上展示了成熟的28nm和40nm设计服务及国内外实际量产案例,引发专业观众浓厚兴趣。

“55nm创新工艺制程(CS250L和CS250S)推出后中国客户的反馈非常好,这和我们当初推出时的定位策略有关,如55nm transistor不变,65nm IP可以重用等,这使得以前65nm客户可以很容易导入55nm制程。现在已经有2至3家消费类电子的用户在使用了,预计明年初将会有3个Tape out。” 富士通半导体ASIC/COT业务市场部副经理刘哲女士介绍说。

如果说高性价比的55nm创新工艺制程是为了一解处于激烈竞争中的本土中小客户IC设计之“渴”,那么此次富士通半导体带来的成熟已经量产的28nm半导体制造技术则是为帮助中国IC设计业应对高端先进制程SoC设计挑战而生。

{pagination}

高端制程SoC设计的“N只拦路虎”

当半导体制程进入40nm工艺节点以后,成本成为高端SoC设计企业面临的第一只“拦路虎”。如下图2所示为32nm/28nm及22nm/20nm工艺制程投资的各项费用,其中32nm/28nm工艺的收支平衡(Breakeven)为30-40M units,而22nm/20nm工艺的Breakeven更高达60-100M units,这样高的半导体制造成本不只掐住了中小IC业者的喉咙,也成为高端SoC设计厂商的巨大压力。再加上IP方面不菲的投资以及整合验证,财务风险可谓巨大。

图2. 32nm/28nm及22nm/20nm工艺的Breakeven情况。

虽然迈向尺寸更小的工艺节点实现了集成度和性能优势,但是设计和制造的复杂度也相应成倍增加, 这成为高端SoC设计企业面临的第二只“拦路虎”。刘哲分析道:“28nm使得一切都变得非常复杂:Double patterning、Layout-dependent effects、New interconnect layers、Difficult design rules、Device variation、New transistors等等。而曾经存在于半导体制造工艺中的诸如成本、产量、上市时间、盈利能力、可预测能力、低功耗(面积)、复杂性等各种问题现在也依然存在,不只存在,当工艺尺寸不断缩小,还会使问题变得更加糟糕。”

此外,不要忘记:Multi-source IP、混合信号和RF、3D-IC方法、系统级封装等这些新的设计方法也会使SoC设计面临更多的挑战。

{pagination}

已量产的28nm技术独占鳌头

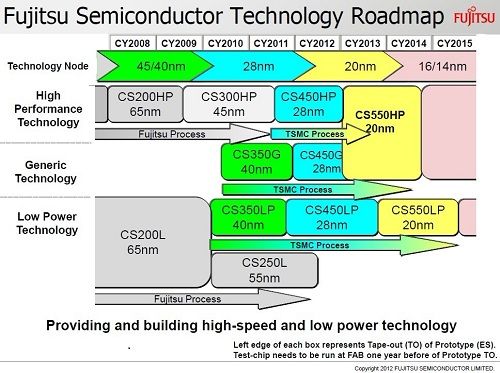

早在上世纪90年代,富士通半导体就在中国大陆开始推广ASIC方案和设计服务。针对不同时期不同的市场需求,该公司都有与之相适应的ASIC方案和设计服务。在本次ICCAD上,富士通半导体展示了其技术路线图并重点展示了帮助中国高端SoC设计厂商克服上述40nm/28nm先进工艺制程设计挑战的成熟技术和已量产实际案例。

图3. 富士通半导体的高速及低功耗技术路线图。

在世界范围内,富士通半导体在40/28nm高端制程上的设计能力相比其他设计公司具有很大优势,并且富士通半导体在28nm IP上也处于领先位置。

和TSMC的密切合作是富士通半导体在28nm上的优势之一。“富士通半导体在TSMC的28nm工艺上的Tape out数量也是名列前茅的,这使我们在对工艺制程的管理、优化方面积累了大量经验。”刘哲介绍说

例如刚开始的28nm工艺可能会有一些良率(yield)不稳定的问题,通过和TSMC的项目合作,富士通提高了量产的良率,包括稳定良率,在这方面取得了非常大的成果,这也是其若干客户先进设计项目能够量产的一个很重要因素。

“量产与否,在半导体设计和制造领域是有质的区别的。现在市场上宣称有28nm项目的设计服务厂商不少,但真正拥有能够进入量产的28nm设计经验的可以说是寥寥无几。而富士通半导体此次宣布的成熟已经量产的28nm创新工艺技术(CS450HP、CS450G、CS450LP)正是为了将先进的高端ASIC方案和设计服务带给中国厂商,以填补国内市场在这个领域的空白。”刘哲表示。

{pagination}

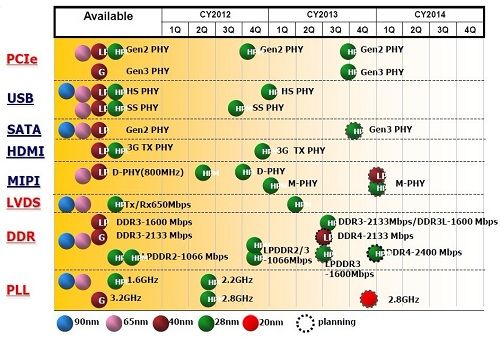

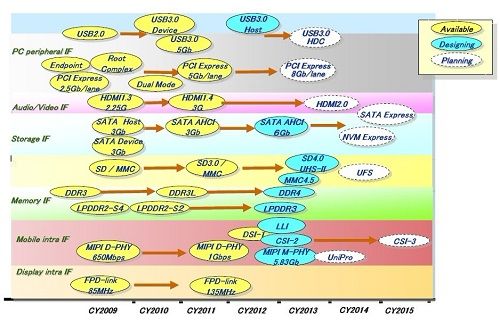

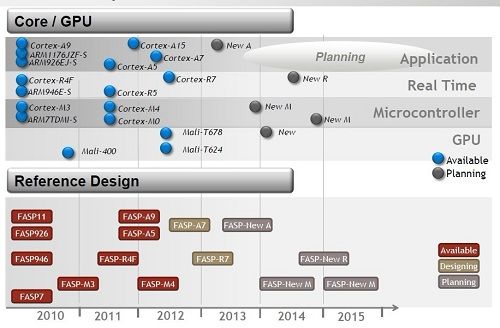

IP的关键词——广泛性、高质量

不只在设计方面领先,在IP方面,富士通半导体也走在业界前列。富士通半导体提供种类齐全的完整IP系列,诸如USB、HDMI、PCIE、SATA、MIPI、ARM CPU、AD/DA等等,其经过验证的28nm IP更是处于业内领先。以下3张图比较全面地展示了富士通半导体的IP。

图4. 富士通半导体领先的28nm IP引人注目。

图5. 富士通半导体IP路线图:Peripheral IP/Functional IP。

图6. 富士通半导体IP路线图:ARM Core。

富士通半导体的IP分为两种,一种是富士通半导体自己开发的IP,另一种是从第三方购买的IP。在对IP的管理上,富士通半导体有它独特的流程和方法,即IPV (IP Verification flow),遵循这样独特的设计和验证流程就可以保证打上富士通Logo的IP的质量。这样就在客户和第三方IP提供商之间又加了一道保险。

“举个例子,富士通半导体和其他设计公司对IP设计要求的标准不同,我们验证的corner会特别多,要求非常严格。这样要pass这么多的corner,就一定要设计出非常有质量的IP才可以,这是和其他公司的不同。还有验证平台的成熟度,验证的覆盖率都是决定IP质量的关键因素,而富士通半导体本身又是一个IDM的公司,我们有自己的IC产品,对产品的严格质量管控是长久以来的传统和立身之本。这也适用于我们的IP和我们为客户定制的ASIC。”富士通半导体刘哲表示。

此外,富士通半导体经过严格评估和量产验证的广泛IP能够省去客户去和不同IP供应商谈判的精力和时间。由于富士通半导体拥有众多合作伙伴和非常大的客户群,因此能够拿到更具优势的价格,这对资金压力巨大的SoC设计厂商来讲无疑非常重要。从芯片的风险角度讲,一旦芯片出现IP的质量问题,客户也无需为此而在各个IP供应商之间周旋。从成本角度,富士通半导体所提供的打包IP方案也会帮助节省客户初期的IP 投入。

{pagination}

通信、消费、高性能计算领域的成功案例

事实胜于雄辩,刘哲通过3个典型的客户案例展现了富士通半导体在高端工艺设计上的技术实力。这3个例子分别属于三个不同的领域:通信、消费电子、高性能计算,并且均已实现量产。而这三个领域都是富士通半导体的传统优势领域。

富士通半导体是目前100G波分复用网络的主要芯片设计方案提供者,是推动100G网络商用的重要力量。刘哲举第一个例子就是富士通半导体的一个基于标准CMOS技术,使用TSMC 40nm工艺的,世界上最快的56G 65Gsps ADC IP。据悉,此IP为光网络传输中100G波分复用网络的核心,已被国内外领先光通信厂商所采用并量产,它的使用使得世界范围内的100G传送网比预期提前两年实现商用。

图7:世界上最快的56G 65Gsps ADC IP。

特别值得一提的是独特的金质底盘封装(图7)。之所以要采用这样独特的封装,是因为类似这样的通信网络可能有亿万门的逻辑,不论是从设计规模还是功耗都很具有挑战,所以不只对芯片本身的设计有要求,对芯片封装的设计也有非常高的要求。金质底盘是富士通半导体特别针对高功耗的芯片而特别设计的,此金质底盘的Substrate有19层,这是业界非常领先的技术,也是富士通半导体所独有的。

第二个例子是世界上第一个采用28nm HPL(高性能低功耗)工艺的LTE/3G/2G 基带IC(用于手机) ,来自排世界TOP3位置的通信厂商。由于特别使用了富士通半导体开发的低功耗methodology,其动态功耗降低了30%。

此外,在设计方面,此基带LSI还采用了富士通半导体的一系列IP,包括ARM11、DigRFV3、V4、HSIC、USB2.0等等。

第三个例子是更加典型的28nm应用,即今年中刚发布的富士通半导体与Oracle合作开发的第10代处理器——SPARC64 X多核多线程处理器,它含有16个内核,每核双线程,在TSMC High Performance工艺上开发。面向服务器等高性能计算领域,处于世界领先地位。的,富士通半导体的SPARC CPU在国际上高性能计算领域很有代表性。

图8.富士通半导体与Oracle合作开发的高性能处理器SPARC64 X。

“随着中国设计能力的提升,这些目前还很先进的技术在国内的需求也逐步多起来,我们也看到了这种需求。所以透过此次ICCAD,富士通半导体通过展示这些有代表性的成功案例,希望可以和中国的潜在客户进行交流,寻找合作的契机。” 富士通半导体亚太区研发部副总裁Vincent Shen表示。

{pagination}

系统方案节省客户前期IP验证时间

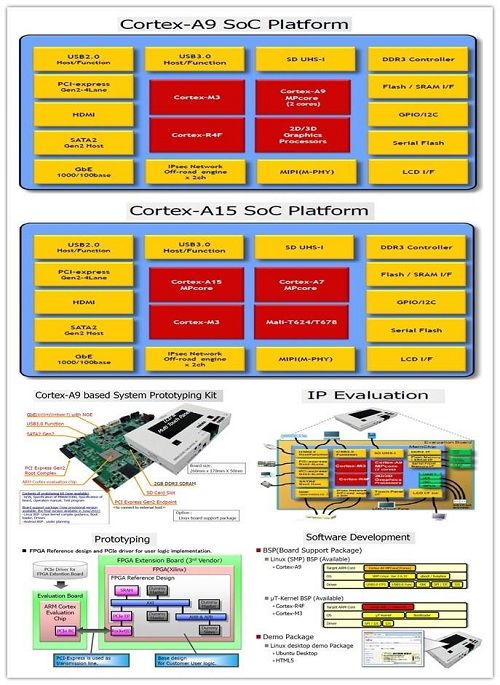

此次ICCAD,富士通半导体还带来了富士通半导体的系统解决方案,包括ARM-SoC Platform和系统原型开发套件(System prototyping kit),也引发中国IC设计业界的热情“围观”。如下图9所示。

图9. 富士通半导体系统方案。

富士通半导体系统原型开发套件可以对Cortex-A9平台以及各种集成IP如CPU和外设进行评估;在ASIC开发的早期验证期间对IP的质量和互操作性进行评估,包括:PCIe/SATA/USB3.0/GbE;CPU效能的评估:Cortex-A9、R4F、M3。还能提供S / W开发:样品的Linux驱动程序和OS移植服务。

“以前客户自己搭平台验证费时又耗力。现在有了这样的平台将会大大缩短SoC设计前期的验证时间,包括客户自己搭平台的时间也节省了,对客户非常有意义。并且富士通半导体还能针对不同客户的需求提供额外定制服务。”富士通半导体相关负责人表示。