作者:武国胜

产品策略总监

四川和芯微电子股份有限公司

高速串行总线技术在电子数码产品中的应用越来越广泛,但事实上,此类技术在市场应用中的潜力尚未得到完全发挥。在未来很长一段时间内,基于高速串行技术的SoC应用将依然是数据传输的主流研发趋势,其中USB3.0作为一个得到业界广泛支持的接口标准,将是市场应用最成功的串行接口标准之一。

四川和芯微电子股份有限公司(IPGoal)今年上半年推出经过USB IF认证的USB3.0物理层IP解决方案。本文将阐述如何基于IP解决方案实现USB3.0的芯片设计升级。

USB 3.0应用趋势与技术挑战

USB 3.0在为消费者提供其所需的简易、快捷的连接性方面正在发挥极其重要的作用。例如,一个采用USB 3.0接口的闪存驱动器可以在15秒钟将1GB的数据转移到一个主机,而USB 2.0则需要43秒。

新的USB 3.0在保持与USB 2.0的兼容性同时,还提供了下面的几项增强功能:

* 极大提高了带宽,高达5Gbps全双工(USB2.0则为480Mbps半双工);

* 实现了更好的电源管理;

* 能够使主机为器件提供更高的功率,从而实现USB电池充电、LED照明和迷你风扇等丰富的应用;

* 能够使主机更快识别器件;

* USB 3.0协议使得数据处理的效率更高。

但目前,对于SoC上的USB3.0应用研发还面临着诸多来自前端技术支持上的挑战:

USB3.0 IP核在架构上包括USB2.0和USB3.0两个部分,就SoC厂商来说,以往的经验已经不足以支撑全新架构下的SoC应用设计。

由于高速IO有物理层(PHY)部分的设计,因此对于IC良率的影响很大,通常将PHY包入SoC内,往往这是量产良率最大的杀手。所以如何通过模拟设计“design margin”的综合考虑,维持量产良率,对IC设计公司而言是相当大的挑战。同时,如何克服硬件兼容性也是相当具有挑战性的问题。

而对于IP供应商来说,如何保证IP核到了SoC的应用中正确,也是目前基于USB3.0 IP应用设计的难题。因为通常在设计中如果出现了问题,究竟是IP的问题还是SoC设计本身的问题?如何界定责任?如何测试到问题所在?在缺乏检测手段的时候,如何检测是IP功能特性没有实现?或者还是制造缺陷、工艺缺陷?……这些都将是非常困难的。

前端技术支持及可靠性非常重要

与纯数字IC设计相比,高速串行接口从480 Mbps至目前的5 Gbps极大地考验IC设计公司在模拟设计与混合信号设计的能力。这也是为什么只有少数公司能设计出USB 3.0完整的产品与IP解决方案的原因。

以信号完整性为例,USB3.0兼容性测试要求5Gbps的信号在通过一条3米长的USB线缆之后,仍旧能够达到抖动容限(40ps)的测试要求,这种测试的要求远超出PCIE或者SATA的协议标准规范。因此,USB3.0物理层IP核的设计主要问题是解决系统级和芯片级的信号完整性问题。如果没有达到这样的抖动容限要求,SoC厂商的产品在恶劣条件的误码率会大大上升,链路失效,从而导致传输数据不稳定,使系统可靠性下降。

在芯片级的ESD保护方面,ESD保护组件必须同时符合下面四项要求才适合用在USB3.0端口:

* ESD保护组件本身的寄生电容必须小于0.3pF;

* 保护组件的ESD耐受能力必须足够高;

* 在ESD事件发生期间,保护组件必须提供够低的箝制电压,不能造成传输数据错误或遗漏;

* 保护组件动作后的导通阻值必须足够低,组件在遭受高能量ESD攻击时仍能保持低箝制电压,以避免出现保护组件未受损但系统内部电路已无法正常工作甚至损坏的情况。

IPGoal采用与工艺相关的ESD设计,在多数工艺条件下均可达到4,000伏的HBM ESD指标。高于业界普通的2000伏标准,增加系统级的可靠性和稳定性。

{pagination}

IPGoal提供优化的USB3.0 IP解决方案

IPGoal USB3.0 IP解决方案具有如下关键特性:

* 完全与PIPE3接口兼容;

* 实现了接收器自适应均衡以补偿通道损耗、串扰和码间干扰(ISI);

* 可编程发送幅值、预加重和压摆率;

* 支持不依赖外部器件的扩频产生与接收;

* 支持USB3.0所有的节能模式(U0、U1、U2和U3),可以实现超低功耗工作模式。

该方案还针对多种工艺进行了设计,可以应用于针对0.13微米、90纳米和65纳米工艺节点的IC设计。目前,市场可用的第三方USB3.0 IP解决方案基本上是针对90纳米及65纳米等高速工艺设计,很少有适用于0.13微米工艺的同类IP,这是因为90纳米以及65纳米设计实现相比,0.13微米的USB3.0实现方案主要挑战在于5Gbps的速度几乎接近了该工艺下半导体技术所能实现的极限。

同时,IPGoal的方案还不乏一些局部设计上的技术优势。例如:一些竞争解决方案可能还需要外部参考器件提供内部参考偏置,而IPGoal已经在IP中解决了这个问题,在降低系统BOM采购成本的同时,也减少了芯片封装的开销;采用特殊电源控制技术,合理分配3.3V及1.2V的功率消耗,降低系统总功耗。

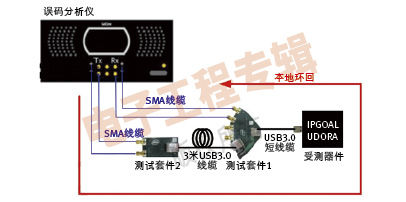

此外,在IP内部,IPgoal设计了全套完整的内建自测平台,可以覆盖IP本身的功能与特性测试。在SoC芯片系统测试时,该平台可用于检测IP的功能与特性,并对工艺缺陷、制造缺陷进行筛选。同时,利用现有的USB3.0 PHY的测试芯片和测试子板,可针对客户的SoC验证平台进行定制化开发,帮助客户完成USB3.0物理层与其系统的联合仿真测试及系统应用,在系统级保证IP与SoC的接口结合。

图1:IPGoal的解决方案通过了USB IF认证,基于该IP开发的IC产品可以轻松通过此认证。

本文来自《电子工程专辑》2012年9月刊,版权所有,谢绝转载。