摘要:本文介绍使用Cypress的PSoC3 UDB实现对异步SRAM的读写控制,并以CY7C1069AV33 SRAM为例介绍其软硬件设计过程。

1, 概述

Cypress PSoC3使用基于单循环流水线的高性能8051内核 (67MHz/33MIPS),提供业界广泛采用的5.5V至0.5V电压范围和低至200nA的休眠电流,可以满足极低功耗的应用场合。PSoC3的高性能模拟子系统和数字系统都拥有可编程通路,允许将任何模拟或数字信号(包括可编程时钟)分配到任何通用I/O引脚,这为使用者提供了真正的“系统级”可编程能力。

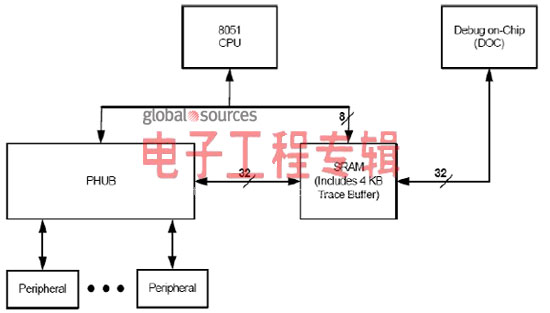

PSoC3中SRAM的容量最大为12KB(3个4KB块),8051 CPU和DMA控制器均可访问SRAM。如果访问不同的4KB块,8051和DMA控制器可同时访问SRAM。图1为PSoC3访问片上SRAM框图。

图1,PSoC3访问片上SRAM

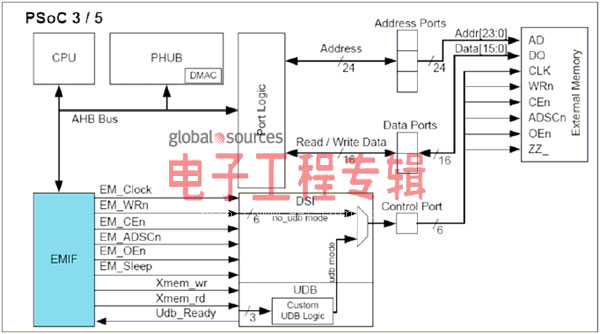

PSoC3同时也提供了外部存储器接口(External Memory Interface, EMIF)用来连接外部的存储器设备。它与UDB、I/O端口和其他硬件产生外部存储器地址和控制信号。EMIF支持同步和异步存储器,但在同一时刻只支持一种存储器类型。其结构如图2所示。

图2,EMIF结构框图

从图2可以看出,CPU和DMAC都可访问SRAM。若数据来源于其他外设比如ADC或者UDB,则数据传输到SRAM的速度将受到CPU或DMAC的限制。因此,在这些数据来源于外设并有传输速度要求的应用中,若采用EMIF可能无法满足其要求。这时可用PSoC3的UDB实现SRAM的读写控制,以实现与外设数据直连。

详细全文请见pdf文挡:基于PSoC3 UDB的异步SRAM读写控制

作者:田江学

主任应用工程师 赛普锐思半导体(上海)有限公司