作者:Erik Mentze

高级系统工程师

赛普拉斯半导体

任何频率合成器的目标都是根据一个给定输入参考频率产生一个期望输出频率。然而,可用输入频率和所需输出频率之间的关系并不总是显而易见的。总会有很多问题出现:我有没有选择最好的频率合成技术参数?可能还有另外的设置可以使频率更干净、电源消耗更少?有时候问题很苛刻,现有硬件是否能满足新的需求(存在解决方案吗?)。本文将介绍一种方法可以找到所有可能的锁相环配置(使用整数分频PLL),这些配置可以满足给定的输入/输出频率要求。运用一个完整的配置列表,为您的特定应用确定最佳配置。

在我们准备为锁相环找到最优配置之前,首先要考虑如何找到锁相环的任一配置。特别是,我们需要能够找到可以用于给定参考振荡器和期望输出频率的所有可能的锁相环配置。一旦我们能够产生满足需求的配置清单,我们就可以选择出哪一个是最好的。实际上,确定PLL 最优配置的大部分工作是确定所有的满足我们需求的配置清单。因此,本文首先将集中在确定所有可能的配置方面,然后讨论如何选择最佳参数。

整数分频锁相环频率合成技术概述

最基本的情况是这样的,任何频率合成器的目标是,基于一个给定的参考频率,来产生一个期望的输出频率。如下方程所示:

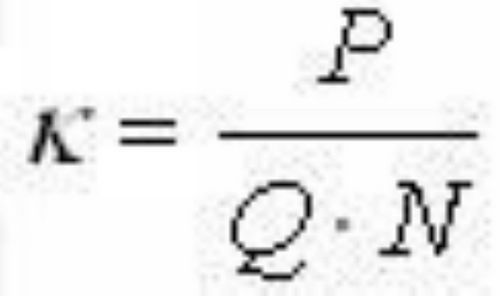

这里K是频率缩放常数,有时参考为常规频率。任何频率合成电路都是一个简单的K逼近机制。本文将不会介绍K产生方法。这里我们将只专注锁相环频率合成器整数分频。锁相环频率合成器通过在参考振荡器和输出时钟之间插入分频模块来逼近K。然后,并使用一个带相位检测器的反馈回路来维持两个分频器相位一致,期望频率就生成了。结构框图如图1所示。这是一个电流泵整数分频锁相环的常用形式。

图1:整数分频PLL的基础方框原理图。

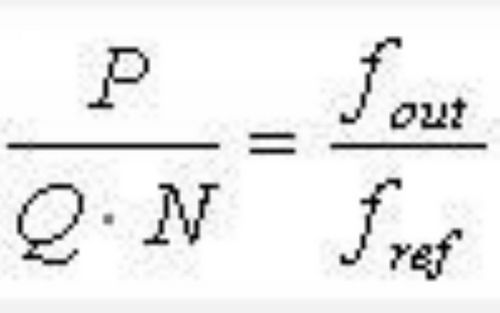

结合方程1和2,输入和输出频率之间的关系为:

图1所示的 常见简化方式是设置N等于1,或Q等于1,或两者都等于1。这些简化都是基于系统设计需求。图1中,所有这3种简化方法都是一般情况下的子集。如果Q和N都设定等于1,那么输出频率的最大分辨率被限制为参考频率,这使得有可能只能整数倍数合成参考时钟。在这种情况下,确定P值就变成了一个简单的算术。如果只是设置Q或N之一等于1,那么只有一种配置存在(考虑最小化Q/P或N/P比值),来合成期望的结果。下一步就是确定比率了,尽量降低分数值。

使用三分频模块,一般情况下会给硬件引入一个额外的层,可以通过为很多不同的频率合成技术应用编程来直接重新使用PLL。然而,这通常也会导致在确定P,Q,N值问题上更复杂。确切地说,结果会造成对现有单个参考和输出频率的多个配置,所有这些配置都有完全不同的性能特点(功耗,起始时间,抖动,相位噪声,等等)。

在可编程片上系统里通常用的附加配置可以有多个输出分频器。这也可合成多个不同输出频率(但仍是VCO的整数倍)。图2显示了这种配置。

图2:带多输入分频器的基本整数分频PLL的方框原理图。

{pagination}

找到可编程PLL所有的可能配置

那么,给定一系列系统需求,我们如何为P,Q,N选择分频值?我们看一下方程3,和前面稍有不同,把所有已知值放在了右面,未知值放在左面。

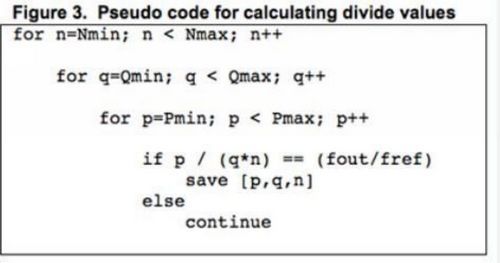

方程4求解的困难是,对于任何任意参考和输出频率,都有三个变量(仅受P,Q,N可选的分频器值范围限制)。方程4求解最常见的方式是使用搜索算法。这种算法通过搜索区间内解,找到适合的P,Q和N值,这就找到了期望值。本质上是三重嵌套环路,搜索所有可能的P,Q和N值。这种搜索算法应用于大多数PLL配置软件。如何实现这种算法的伪码基本实现如图3所示。请注意,还要把很多实际的系统约束加到代码里,这样才能根据有用的配置做出可靠的产品。

图3:描述分频值算法的伪代码。

使用三分频模块来接近K值:参考分频器(Q),反馈分频器(P),输出分频器(N)。我们可以看出,在这种类型的频率合成器中K定义为:

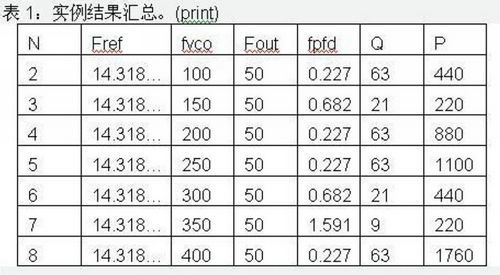

举一个例子,我们将从14.3181818…MHz 参考时钟(一种常见的视频信号频率)合成一个50MHz输出。假设压控振荡器的频率范围是100MHz - 400MHz。使用类似图3的搜索算法,可以产生如表1所示结果。所有满足我们要求的可能配置都显示在表里。现在我们需要做的就是选择最佳配置。

表1:实例结果汇总。

选择最佳配置

现在我们找到了所有可能的满足我们需求的频率配置,我们可以将注意力放到选择性能最优参数上。最佳配置完全取决于应用。例如,对于远程监控系统,需要快速启动器件,但不需要很精确。对于通讯协议,可能不需要注意启动时间或功耗,但要特别注意时钟源抖动问题。或者两者都需要注意到:收集数据时只需快速唤醒,数据通信期间需要高精度。使用可编程PLL和可编程片上系统,你就可以两者都兼顾到。只需要知道需要哪种配置就可以了。

下面我们讨论一下在不同应用中需要优化的几个参数。表2总结了这些参数,相应的关键回路参数,以及如何优化。请注意,并不是所有的可编程PLL都可以访问下面参数。

表2:可编程PLL优化参数。

功耗

功耗受控于压控振荡器频率、电流泵电流、分频器模块设置。大多数压控振荡器结构需要比较大的尾电流以达到更高的频率。这就意味着随着频率的增加,功率消耗也会提高。电流泵电流每个PFD周期放电一次。当需要较大的电流泵电流时(用于循环稳定或快速启动/建立时间),每个PFD时期会有更多的功耗。时钟分频器在每个时钟沿消耗功率。时钟分频器值越大,就需要更多的分频器单元来传输,这就消耗了更多的功率。

{pagination}

启动时间/建立时间

一个电流泵锁相环的启动和建立时间是由固有循环频率决定的。该参数可以视为是速度慢了的锁相环频率。它来量化锁相环可以改变输出频率的速度。它和压控振荡器增益和电流泵电流是成正比的,和反馈分频器值和环路滤波电容是成反比的。为了最小化启动时间,就需要最大化压控振荡器增益和电流泵电流,最小化分频反馈设置和环路滤波电容。

抖动

类似于启动时间/建立时间,PFD频率和压控振荡器增益在其中扮演了关键角色。PFD频率越高意味着锁相环环路滤波器电压刷新频率越高。这就防止了环路滤波器电压漂移。使用大的环路滤波电容, 每PFD周期电压漂移量会降低到最小程度。因为压控振荡器增益决定了环路滤波器每单元电压漂移对应的输出频率漂移量,压控振荡器增益越低,锁相环对环路滤波器电压漂移越不敏感。

相位噪声

优化相位噪声和应用关系密切,大体观察就能看到。通常,由参考振荡器引起的相位噪声,可以通过将锁相环设置为较低的闭环带宽方式来减小。由压控振荡器引起的相位噪声,可以通过将锁相环设置为较高的闭环带宽方式来减小。

可以控制用来减小相位噪声的一个参数是输出分频器(N)。相位噪声分频器和输出分频器设置成正比。如果输出分频器是低噪声分频器,那么压控振荡器就运行在较高的频率,并将输出频率降低来使相位噪声得到改进。

实例优化

最后,讨论一下在上面的例子中如何优化锁相环的一系列配置。

功耗

如果低功耗是设计关注的重点,我们希望减小压控振荡器频率和分频器值。N = 3,Q = 21,P = 220将是最好的选择。这种设置可以使压控振荡器工作在更低的频率,更低的P和Q值,并有一个合理的PFD频率。

启动/建立时间

如果启动/建立时间是主要关注的,那么从表1中很明显可以看出,N = 7,Q = 9,P = 220是最理想的配置。它的fPFD 是任何其它配置的2倍,从而在环路滤波器电压有较高的刷新频率。

抖动

如果低抖动是首要关注的对象,那么N = 7,Q = 9,P = 220是最可取的配置。它的fPFD 是任何其它配置的2倍, 从而在环路滤波器电压有较高的刷新频率,那么这是所有可能的配置方法中抖动最低的。和优化启动/建立时间不同的是应该为低抖动选择较大的环路滤波电容和较低的Kvco 。

相位噪声

优化相位噪声是高度依赖于应用的,这取决于特定参考振荡器和压控振荡器的噪声性能。基于配置列表,我们可以做的是选择较高的压控振荡器频率,这样就能使相位噪声降下来。N = 7,Q = 9,P = 220可能是最好的,因为它的PFD频率很高,远高于N = 8,Q = 63,P = 1760的配置。如果环路具有较高的抖动,那么相位噪声面将显著提高,就会掩盖输出分频器给我们带来的任何改善。

本文来自《电子工程专辑》2011年10月刊,拒绝转载。