摘 要:本文通过对串行传输协议的研究,提出了一种适用于微控制器(MCU)低成本测试的数据串行压缩传输方法。该方法用较小的电路面积实现了片上接收端逻辑,并通过对发射端压缩算法的优化,实现了超过30%的传输时间缩减。

1.引言

随着半导体芯片特别是ASIC测试技术的发展,微控制器领域为追求更低的测试成本,也从早期的基于CPU指令级的测试实现了向可测试设计(DFT)的转变。扫描设计(Scan Test)、边界扫描设计(JTAG)、BIST(Built In Self Test)等技术使得在同等测试品质下,测试难度及测试时间均得到大幅降低。但由于MCU架构复杂、宏单元多的特点、传统的可测试设计难以做到全覆盖。以嵌入式闪存(FLASH)为例,不同于随机存取存储器(RAM)嵌入式闪存的测试有着复杂的流程。传统上仍然需要编制CPU程序实现这一测试。非同期设计的IP,模拟类宏单元、系统模块等的情况也是一样。由于难以实现一般意义上的可测试设计,编制CPU程序进行测试是默认选项。

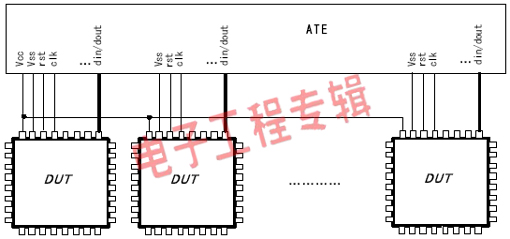

依赖于CPU程序的测试,首先必须面对的如何读取测试用CPU程序的问题。早期的MCU通常采用两种方式:一)使用外部存储器扩张模式,即放置在芯片外部,CPU边取指令边执行的方式。二)使用外部存储器扩张模式或类似模式,传输程序至片上RAM1,再转至RAM上执行的方式。方式一的优点是程序结构简单无需额外的片上RAM,缺点是由于外部扩张时总线周期长,对于执行周期较长的程序测试时间也会变长。方式二则利用了片上RAM总线周期短的优势,一定程度上克服了方式一的缺点。随着MCU搭载片上锁相环 (PLL)越来越成为主流,MCU核心包括RAM可以有远高于外部总线频率的片上工作时钟。这使得上述两方式之间的测试时差进一步扩大,方式二逐渐成为首选。工艺的进步﹑核心频率的增加使得在片上RAM上执行的测试时间不断得到缩减,但限于测试条件及测试机性能等因素,传输CPU程序至RAM的过程并没有得到明显改善,并越来越成为一个瓶颈。图1是利用多个芯片同时测试Multi-Die Test)以降低单位测试时间的一种少管脚低成本测试方案。为了最大化利用测试机的测试通道,测试用端子做了最大程度的削减,用于传输CPU程序代码的端子仅为一根。程序代码的串行传输使得本就成为测试瓶颈的传输时间问题更显特出。

图1:多个芯片同时测试(Wafer sort with Multi-Die Test)

详文请见pdf文挡:面向MCU低成本测试的数据串行压缩传输方法

作者:唐乃坚

瑞萨集成电路设计北京有限公司苏州分公司