SoC技术为IC产业和IC应用技术提供了广阔的市场发展空间,也成为应对电子产品愈加紧迫的产品上市时间的有效解决方法。但同时,SoC设计也为IC开发人员带来诸多挑战,SoC设计需要运用IP核复用技术、深亚微米技术和软硬件协同设计技术,此外,还面临低功耗设计、可测性设计等技术挑战。随着半导体工艺技术向更先进节点迈进,IC设计公司在设计到量产的流程中,不仅要承受更大的技术挑战和风险,还要应对日益攀升的流片费用。为了降低开发风险、提高设计效率,不少IC设计企业开始与专业集成电路设计服务公司合作,这也进一步带动了SoC设计服务市场的发展。

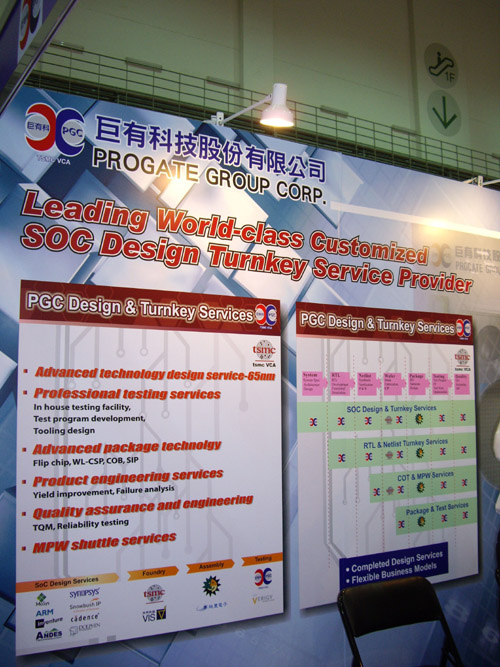

图1:巨有科技拥有19年的IC设计服务经验

作为台湾第一家ASIC设计服务提供商,巨有科技(PGC)的发展历程也印证了上述产业趋势。巨有科技(PGC)创立于1991年,致力于提供SoC/ASIC设计的Turnkey服务,该公司是台积电(TSMC)的价值链整合伙伴(VCA)。随着SoC芯片集成度不断提高,改善设计成本、设计时间并提升设计成功率已成为SoC设计的发展趋势,SoC具备高集成度的复杂性,设计流程必须兼顾软硬件协同设计,并行处理设计流程变得愈发重要。为应对这种趋势,巨有科技建立了并行处理设计流程,以构建具有时间及成本效益的SoC设计流程,藉此将ASIC设计服务提升到SoC 设计服务的层级;此外,巨有还建立IP复用库,验证及侦错采分向独立作业,以减少工程人力耗费,并加速产品上市时间,并通过在SoC设计模块内建BIST,以削减测试成本与时间。

“巨有从各种IP的提供、RTL coding到系统整合,使用先进完整的Synopsys 65/40nm 设计流程,还整合了Cadence、Mentor Graphics等厂商的EDA工具,完全符合TSMC Process的认证。”巨有科技专案管理部专案经理叶佳政介绍,该公司自建无尘室(class1000),拥有Agilent 93000 SoC, Chroma 3650 与Credence D-10提供完整的测试设备(C/P、F/T、FA…等),从测试程序开发、工程验证到大量测试均可完全涵盖,测试产能:C/P每月可达8000片晶圆片、F/T每月可达8百万颗。

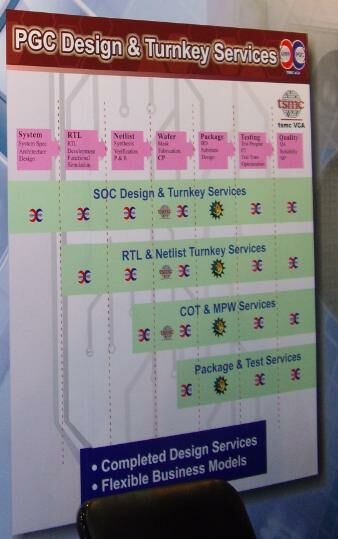

图2:巨有科技提供SoC设计服务整体解决方案

“巨有科技提供的定制化SoC设计整体解决方案包括:ASIC Design、Platform ASIC、RTL to GDS Design、MPW & COT Design以及SiP Design Turnkey等完整服务。”叶佳政介绍,巨有与许多国内外IP公司建立长期稳定的合作的关系,积累许多IP使用、整合、验证的技术经验,也可以为客户订做各种IP。

据巨有科技行销业务部专案经理郑大宗介绍,从1991年创立至今,巨有科技已经为数百位客户成功地完成超过950个项目,累积超过数亿颗IC量产以及数万片的晶圆片实务经验。产品应用范围涵盖了3C产品、工业自动控制、车用电子、航天科技、RF、安全监控、数据储存等各项应用电子产品,超过数亿颗IC量产经验以及数万片的晶圆片,并且销售到欧洲、美国、日本、以色列、俄罗斯、韩国、台湾和中国大陆等世界各地。在2008年巨有科技已具备90纳米半导体工艺的技术,并支持设计完成数个IC的项目,在2010年有数个 Platform ASIC design in并且 Tape out 了数个65纳米项目。

图3:巨有科技参展IIC-China 2010秋季展