市场分析人士预测,与去年比,今年DRAM营收的增长将超过70%,而且未来将越来越多地采用DDR3内存。一些市场情报机构甚至预测,今年DDR3器件会短缺,而且这种状况还会延续到2011年。

美光科技(Micron Technology)公司已为不断增长的DDR3市场需求做好了准备。该公司最近推出了一款基于40纳米节点技术的2Gb DDR3 SDRAM,UMB TechInsights公司对其进行了详细分析。

在不到一年内,相继推出DRAM的两个新技术节点确实是个巨大成就,尤其对于50纳米以下节点。在这种工艺技术水平上,先进光刻技术对预算的需求开始不成比例地升高。制造商必须在工艺成本、工具集以及改造、缺陷检测策略和设计规则等方面进行审慎权衡。

为了成功升级工艺节点,DRAM制造商必须在如下方面持续投入:致力于降低运营费用并保持生产基地的成本竞争力;研发投入以及加大其知识产权储备;扩展现有工艺技术或引进可扩展至未来节点的新工艺。

美光成功地实施了这三项原则。该公司扩大了与DRAM制造商南亚科技(Nanya Technology)的合作,并提升了制造竞争力。没有创新就不能迅速推出新技术,所以一个强大的研发团队和不断丰富的专利集是非常重要的。

美光的70、60和50纳米节点都使用类似的工艺流程,采用三层金属、四重聚合物CMOS工艺制造,具有凸起的源/漏区。该工艺的金属层3和2采用的是铜、金属层1采用的是钨;外围晶体管则由带钨包层的第一层聚合物、氮化钛隔绝层、氮化的栅氧化物、用氮化物衬底隔绝的浅沟道以及三个阱区组成。

SDRAM单元在一种位线电容结构中使用层叠电容。多层单元板包含聚合物、钨和氮化钛层;电容电介质是一种双层高k电介质;存储节点是氮化钛层;多晶硅附着栓用于电容连接。SDRAM阵列采用带氧化物电介质的凹道排列晶体管(RCAT)以实现更长的有效沟道长度和更低的沟道掺杂浓度。

美光在40纳米节点采用类似的工艺,但有一些重大变化,尤其是在栅堆叠、互连和电容模块方面。电容高度和RCAT深度没有显著变化,不过,对栅电介质厚度,聚合物栓高度和触点宽度以及间距进行了调整以适应工艺升级。

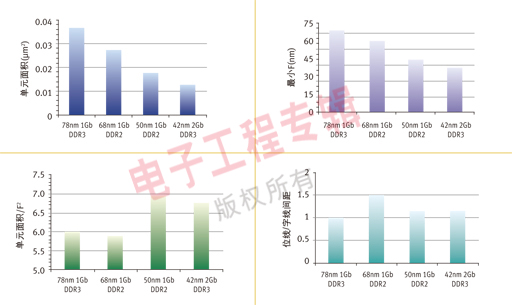

UBM TechInsights对美光40纳米节点DDR3 DRAM器件的全工艺分析详细论述了上述改变。本文着重强调:虽然工艺整合机制相似,但50和40纳米节点明显不同于70和60纳米节点;因为前者使用了诸如浸润式和双图形工艺(double patterning)等先进的光刻技术。从设计角度看,这种工艺缩微仍是个挑战。图1比较了这种工艺缩微对单元大小和字线-位线间距的影响。由半字线间距决定的单元面积和最小F值被系统地缩小了。

为确定布局,单元面积可被表述为:一个常数x F2。单元面积与最小F2之比表示,50和40纳米技术节点并非严格的6F2,而是一个松散的6F2(6.8F2)。位线与字线间距之比表示,位线并不像字线那样会随着节点的不断升级和缩微而变化。不过,与50纳米节点相比,40纳米节点的晶硅效率要好得多,从而能够通过加大晶硅面积、缩小单元尺寸将存储器单元数从1Gb提升到2Gb。

美光DRAM工艺整合的稳步前进得益于该公司在其技术节点早期就实施的四个主要工艺创新:很早就引进6F2布局(连续在5个节点使用); 凸起的源极和漏极以及RCAT(4个节点使用);在DRAM和闪存中很早就采用铜镶嵌工艺(4个节点使用);网状电容(mesh capacitor)。

与8F2布局比,6F2布局可使设计更紧凑。三星首推凹道排列晶体管,但美光的70纳米节点将RCAT概念与凸起的源极和漏极相结合,该办法在解决漏电方面具有优势。

铜镶嵌工艺降低了整体成本,尽管其最初的工艺成本较高。使用铜互连引入了比熔丝技术更优越的反熔丝技术。反熔丝可以很容易地与铜技术整合在一起,而且在工艺上也比金属熔丝更简单,后者是通过图形化工艺以及由钨填充的过孔来实现的。

网状电容是一个由美光和三星各自独立拥有专利的设计概念,它保证了工艺技术的低成本并支持工艺节点缩放。

在4个技术节点中都采用类似的工艺,这点业已证明美光在更好地利用资源方面的优势。但有迹象表明,该工艺可能难以被应用于30纳米以下的工艺节点。

目前,在40纳米节点,在字线方向,两个存储晶体管的间距已小于35纳米;存储节点和金属层-1(位线)的间距也已小于15纳米。这些数字表明,对未来节点而言,漏电可能成为首要问题。

不过,历史上存储器制造商的表现一直超过市场和技术观察人士的预期,因此有理由假定,目前在存储器厂商的研发实验室内,也许正酝酿着出乎人们意料的创新。

图1 美光4代DRAM工艺技术比较。

Arabinda Das

高级技术分析师

UBM Techinsights

本文来自电子工程专辑杂志9月刊,拒绝转载