芯科实验室有限公司(Silicon Labs)Timing产品推出市场以来,因其优异的去抖性能、灵活的任意频点的配置、比竞争对手缩短一半的交货周期而获得广泛的应用。Silicon Labs专利DSPLL技术作为每一款Silicon Labs Timing产品的核心,使Silicon Labs产品具有了超越竞争对手的优异性能。下面将详细介绍DSPLL的原理和特点。

DSPLL的原理

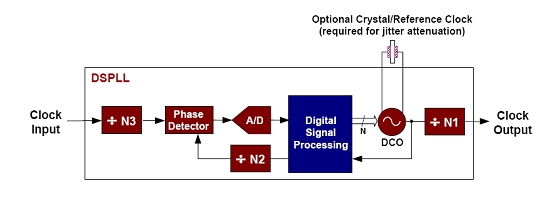

这项技术运用DPS高速运算替代通常采用的分离器件搭建的锁相环滤波电路。由于不需要外接器件,单板的噪声对锁相环影响降低到最低。这项数字技术能够在温度,电压变化和外围MCU不同的情况下提供高度的稳定性和一致性。下图是DSPLL一个简单功能框图。

DSP运算处理Phase Detector的相差脉冲,产生一个数字频率控制字M来调制一个数字控制的时钟DCO。数字分频器N1,N2,N3都有很大的范围,这样可以是在一个输入频率下,产生近似任意频率的输出。具有DSPLL技术的窄环路带宽产品(Si5316, Si5319, Si5323, Si5326, Si5366, and Si5368)提供超低的输出抖动和极强的抖动衰减性能。对于那些需要多路低抖动时钟频率转换的应用,宽环路带宽的产品(Si5322, Si5325, Si5365, and Si5367)是一种很好的选择。

DSPLL带来的优势

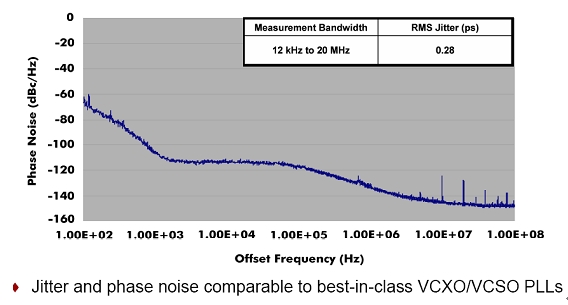

(1)极低的输出抖动0.3ps RMS抖动。

(2)宽范围的输入频率和输出频率。

输入频率:2KHz-710MHz

输出频率:2KHz-1.4GHz

由于数字分频器都有很大的范围,才能保证宽范围的输入和输出频率。在搭建复杂的时钟系统的时候,特别是作为一个时钟平台,应用在各种场合,只需要改变软件和pin的管脚配置就可以完成,而竞争对手的芯片,就需要改变芯片的型号,重新进行设计。

(3)可调的环路带宽。60Hz-8.4KHz,采用DSP技术来做PLL的低通滤波器,带来一个非常大的好处就是可以通过改变寄存器来调节环路带宽,适用于多种信号质量的环境。

(4)极低的相噪指标。 采用芯片内部集成滤波器,可以有效的降低来自单板的噪声干扰。

(5)集成度高,简化了锁相环的设计和布板

传统的锁相环芯片,需要客户自己来设计低通的滤波器,还要做好低通滤波器的EMC 的防护措施,布板的时候也需要特别的注意。由于Silicon Labs PLL外围基本上没有什么器件,仅有一个作为reference 的时钟输入。芯片的设计有DSPLLsim软件完成配置,布板没有强制性要求。

……

供稿:世强电讯