缩短设计时间和提升设计性能是目前提升半导体公司市场竞争力的关键之一。在这里请大家进一步了解一下EDA厂商的动作,以半导体设计、验证和制造的软件及知识产权供应商Synopsys公司推出的Design Compiler为例。

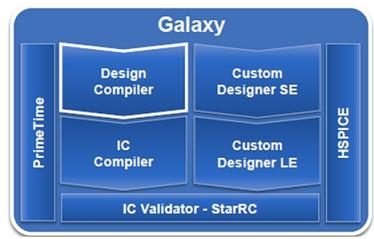

该公司今年初在其Galax设计实现平台中推出了RTL综合工具Design Compiler 2010,将综合和物理层实现流程增速了两倍,来满足日益复杂的设计中极具挑战性的进度要求,帮助IC设计工程师尽量减少重复工作并加速物理实现进程。

图1: Design Compiler成为Galaxy的新成员。

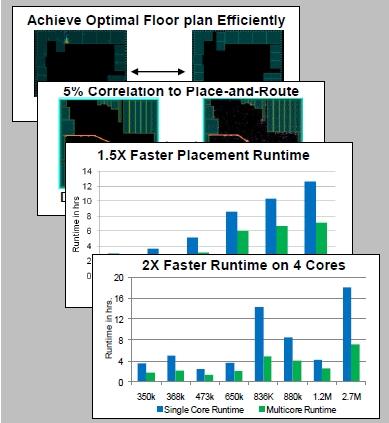

Design Compiler 2010对拓扑技术进行扩展,为Synopsys的布局布线解决方案IC Compiler提供“物理层指引”;在将时序和面积的一致性提升至5%的同时,还将IC Complier的布线速度提升了1.5倍。Design Compiler 2010的这一项新功能使RTL工程师们能够在综合环境中进行布局检测,从而可以更快地达到最佳布局效果。此外,Design Complier采用可调至多核处理器的全新可扩展基础架构,在4核平台综合运行时间可提高2倍。

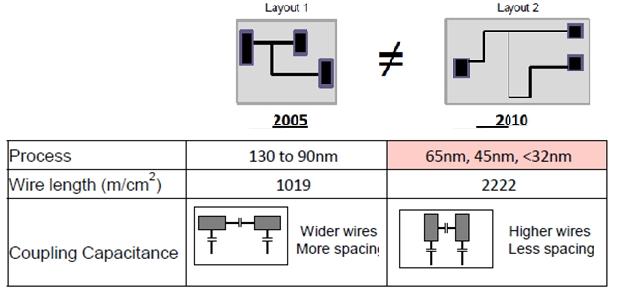

在与Synopsys公司的产品市场总监Priti Vijayvargiya的交流过程中,她多次强调了简化IC设计流程、降低重复工作量,以及在高密度线宽时代EDA支持工具的重要性,他们正在测试该工具在22纳米下的表现。工艺技术的发展使内部连线变短但同时变宽,好处在于可节省更多的空间,但无处不在的互连延迟仍然是高密设计的主要挑战(图2)。她表示,逻辑综合对于包含物理层实现在内的设计收敛加快的影响显著增长,Design Compiler 2010是这种趋势继续延续的具体体现(图3)。

图2: 线宽的提升使互连延迟成为主要挑战。

一些半导体公司,例如Renesas和Realtek,已开始得益于这种高度集成EDA工具带来的高效率。

图3: 性能提高示意图。