即使各公司销售的是封装好的器件和非裸片,但由于各芯片通常采用隔离式的设计,因此可能会导致过度设计,或者太大而无法适配封装。在做芯片级I/O规划时如果不考虑封装或系统其余部分,将会导致过于复杂或无法布线的封装设计,这需多次反复才能达到收敛。

当半导体工艺发展到45nm,以及有更多的功能需要添加到硅片时,问题将变得更加严重。以更高速度和更低电压运行的大量I/O只有提高对封装的要求才能满足性能需求并向芯片提供均衡的电源。芯片设计人员在进行I/O初始规划的过程中必须考虑封装的可布线性、电源供电和I/O行为。要达到这些目标,他们必须将有封装意识的I/O规划与自动布图规划综合(AFS)有机结合起来,这对芯片的平面布图规划(Floorplan)和封装的布局设计而言是极具性价比的方法。

AFS集成了包括锡点布局和RDL(重分配层)布线在内的I/O规划,可以为复杂的分层设计、有拥塞意识的硬宏布局和自动电源规划提供自动划分和整形等功能。这些功能不仅可以节省相当多的运行时间和人力,而且可以提供更好的时序、面积和优质的结果。有封装意识的I/O规划与AFS结合使用后,可以快速开拓设计空间,并提供速度更快和可预测性更高的设计收敛路径。

在45nm工艺节点,越来越多的芯片设计对焊盘进行了限制,并且裸片尺寸直接受I/O规划和排序效率的影响。45nm问题的焦点大都集中在芯片的IP内核方面,因为这是技术实现的关键所在。但45nm内核仍需处理传统器件中的更高电压、更大尺寸和标准接口,因此优化的I/O规划和布局变得越来越重要。

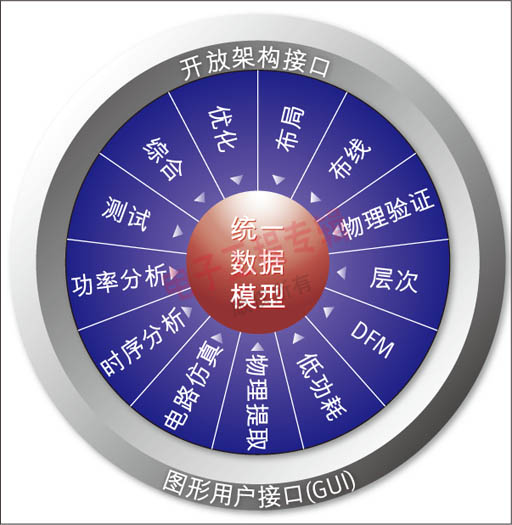

图1:统一数据模型将所有设计元素都添加到综合流程中,从而加速优化过程。

具有封装意识的芯片设计

向45nm工艺过渡的设计人员需要能提供封装概念相关指南的设计工具。目前获得广泛接受的一种方法是具有封装意识的芯片设计。就像平面布图规划是SoC设计的关键组成部分一样,具有封装意识的I/O规划作为完整系统设计流程的一部分有助于满足成本、性能和上市时间压力的需求。I/O规划有助于通过最优的I/O和锡点布局及高性价比封装减少裸片尺寸。前期的具有封装意识的I/O规划结合AFS可以帮助芯片设计人员分析从芯片I/O缓冲器到PCB的互连。

在结合封装意识的I/O规划和AFS技术的方法中,平面布图规划工具能够采用来自封装的I/O信息驱动芯片上的逻辑布局同样非常重要。Magma公司最新的Hydra平面布图规划工具,有助于驱动设计的虚拟扁平簇布局,反过来则影响到工具如何自动调整平面布图规划,并将宏放置到每个块中。这对倒装芯片设计来说尤为重要,因为锡点布局此时将决定平面布图规划的状态。Hydra能够自动获取其系统中的锡点布局和RDL布线,从而提供到I/O的最佳连接。

另一方面,封装的考虑因素会受芯片上的逻辑所驱动。封装工程师应理解设计所表现的限制(如在芯片上布局某些宏),并使用该信息形成最优的I/O布局和封装。

当然,实现之前要考虑的是该技术如何在现有设计流程中发挥作用。答案是设计必须支持工业标准格式,如芯片侧的LEF/DEF和封装侧的APD。用于实现该技术的软件必须能够在所有数据可能不存在以及设计可能不完善的规划环境中运行。因此,拔取、分析和验证工具必须足够灵活和智能才能突破这种限制,从而提供足够精确而有用的结果。

有封装意识的芯片设计的未来方向对封装工程师和设计工程师来说是相同的,他们应该通过使用统一的数据模型来观察I/O规划同时对设计和封装带来的影响。

在设计周期早期引入自动化I/O规划后,I/O性能可以在信号完整性、电源完整性、物理实现和成本方面得到增强。设计人员可以通过优化I/O规划来缩小裸片尺寸和/或完全利用裸片面积。他们可以使用最便宜的封装技术,同时确保性能目标得到满足,并精确估计负载条件以确定驱动强度要求。也许最有用的是,设计人员可以在设计环境中管理芯片/封装连接,而无需使用外部电子表格。

早期的I/O规划对封装工程师来说也很有用,因为它为创建初始封装版图提供了指南。I/O规划打破了芯片和封装的典型顺序性设计惯例,实现了“一次性通过”的设计流程。{pagination}

统一数据模型

统一的数据模型支持芯片和封装作为具有单用户接口的有源器件。它可以用作优良芯片和封装互连矩阵的知识库,在这里芯片和封装的连接性可以得到有效管理。它的功能包括芯片和封装折衷开发,其反馈参数则详细描述了电气和物理约束。统一数据模型通过使用工业标准OpenAccess数据库将所有设计元素集成进了综合流程中,因此可以加快优化过程。

具有封装意识的芯片设计方法的功能包括I/O综合、布局和布线。I/O综合可以创建具有高性价比封装选项的最优I/O规划,同时满足物理和电气约束条件。通过设计校正的I/O环可以用来满足整套约束,包括信号/电源/地(SPG)需求、封装设计规划、内核平面布图规划和板级I/O需求。

AFS可以根据驱动器模型计算特定电压平面的电流要求,并计算需要的球数量。它的多个电压域可以适应设计的每个电源域。AFS可以通过优化I/O环规划来减小裸片尺寸和I/O行面积。如果裸片尺寸是固定的,那么只有存在切实可行的I/O环规划时才能取得成功。

I/O、锡点或绑定焊盘和引脚都是在AFS之前通过布局引擎放置在裸片周围的,它考虑了预置的实例(I/O和/或IP内核)、I/O单元组(如总线I/O)以及电气约束。一旦I/O环完成了综合,AFS就能产生合理的I/O规划。

封装级布线和电压域平面切割要求全部通过设计规划检查(DRC),并遵守封装规划,这对建立有效的芯片到封装网络分配和正确的电源平面锡点/焊球分配来说都是重要的考虑因素。

不要对45nm设计问题视而不见。由于电压更低,因此电源、地以及I/O规划表现出前所未有的重要性。另一个已经被认识到的问题是封装和裸片之间的交叉耦合。在更低的电压时,芯片上的电路更容易受交叉耦合的影响。如果没有把芯片和封装看作单个电路来规划,来自封装的交叉耦合将严重影响芯片的性能。当封装上的布线处于芯片下面时这种现象很容易发生,而禁止在倒装芯片的裸片下布线也不实用,这将可能提高封装成本。

因此具有封装意识的芯片设计必须从项目开始就进行规划,这样才能避免问题、控制成本并实现最优性能。

向45nm工艺过渡的设计人员不必是封装方面的专家,但他们需要封装意识的芯片设计这样的方法来帮助他们理解封装概念。具有封装意识的I/O规划作为整个流程的一部分有助于设计人员满足成本、性能和上市时间要求。

Jayshree Desai

设计实现业务部门

业务开发总监

Yukti Rao

高级产品经理

Magma设计自动化公司