基于DisplayPort的系统必须保护所有可能外露的接口信号和电源引脚,使其能够满足或超过IEC 61000-4-2等级4(±15kV空气放电, ±8kV接触放电)的EOS规范要求而不受损坏,同时还要满足信号完整性方面的眼图指标要求。

DisplayPort就像电视机上的HDMI一样是帮助PC显示高清视频内容的新型图形通信接口。如同HDMI那样,在DisplayPort的设计中也存在着一样的防护问题,这些问题都源于接口信号的高速度、正常使用条件下静电和电缆放电事件等持续的威胁。

DisplayPort标准是一个非压缩的、开放的数字通信接口,该接口通过强化内外部的互联,为PC制造商提供了降低成本的机会。在内部使用时,它是PC或监视器内部的一个接口。在外部使用时,它可以将PC连接到监视器、投影仪或者电视机上。当用作外部接口时,DisplayPort插头常常受到直接来自用户的静电放电(ESD)或由于热插拔电缆引起的电缆放电(CDE)的影响。

为了确保正常的功能,基于DisplayPort的系统必须保护所有可能的外露接口信号和电源引脚,使其能够满足或超过IEC 61000-4-2等级4(±15kV空气放电,±8kV接触放电)的EOS(电过应力)规范要求而不会损坏。

在绝大多数情况下,片上ESD保护是不足以满足该EOS要求的。要满足EOS规范,需要再加片外的ESD防护电路。而标准中支持2.7Gbps和1.62Gbps两种速率,这种高速链路使得防护措施变得更加复杂。在如此高的数据速率条件下,随着DisplayPort一致性测试规范(CTS)的发布,信号完整性和阻抗要求被业界给予了前所未有的关注。

ESD/CDE的前景展望

ESD/CDE事件增加,片上防护能力降低:随着工艺技术的不断发展,接口的ESD防护变得日益困难。对更快处理速度和更高功能密度的强烈需求导致MOS器件的最小尺寸还在不断缩小。2007年初,Intel公司推出了其第一款采用45nm工艺的处理器原型。但随着IC芯片体积越来越小,密度越来越高,功能越来越复杂,它们也变得越来越容易遭受ESD事件的破坏。

以前常采用片上ESD分流结构来保护内部电路免受ESD冲击而破坏。不过随着工艺尺寸的不断缩小,芯片面积越来越宝贵,为了保持芯片性能,这些保护电路只能逐渐地被牺牲掉了。

2007年8月,有关ESD防护目标等级的行业机构提出了一个降低片上IC ESD防护等级的新建议,将目前的2kV HBM(人体模型)/200V MM(机器模型)分别降低到1kV HBM/30V MM,以减轻业界设计高速和高性能IC并将其快速推向市场方面的压力。而系统ESD防护等级仍需满足IEC 61000-4-2提出的要求,即8kV的接触放电/ 15kV的空中放电。因此,虽然精心设计的片上ESD结构仍然能够提供良好的二级保护,但能够符合标准的有效防护必须依赖鲁棒性的片外解决方案来实现。

片外保护之所以必要和重要的另外一个原因与保护器件的位置有很大的关系。通常,片上防护电路距离接口输入点太远。当ESD产生的瞬态信号传播时,会耦合到相邻的导线上,包括数据线、时钟信号线以及电源线。更严重的是,它们的电压幅度会由于Ldi/dt效应[Vpk=Vesd + L(di/dt)]而增加。

电缆放电

像DisplayPort这类的I/O应用还会遭受另一种常见的ESD,即电缆放电(CDE)。这种现象通常在带电的电缆插入到插座中时产生,电位差将引起对电路的瞬间放电,从而导致IC的损坏。只是简单地将电缆从包装中取出来就会对电缆充电,更不用说顺着地毯拖动电缆了,这样会积累更多的电荷。目前还没有颁布CDE标准,但为了从系统级和器件级解决这一问题,业界已经进行了大量的工作。目前的常见做法是按照IEC标准来测试系统。

ESD分级

器件级和系统级的应力模型对比:在讨论DisplayPort设计的特殊需求之前,重要的是要了解各种ESD分级之间的差别。ESD有三种基本模型:人体模型(HBM),机器模型(MM)和充电器件模型(CDM)。HBM又被进一步分为系统级测试和器件级测试,分别由IEC 61000-4-2和 MIL-STD-883所覆盖。这两个标准在ESD一致性方面都得到了业界的广泛认可。但遗憾的是,在一些技术文献中时常会有对这两个标准的错误理解和错误引用。

器件级HBM主要用于确保在ESD受控的制造环境中安全地制造IC。而系统级ESD等级则对系统设计师更为有用,因为它们指出了器件需要提供的系统级保护指标。在器件级的ESD鲁棒性和系统级的ESD鲁棒性之间没有严格的关联。

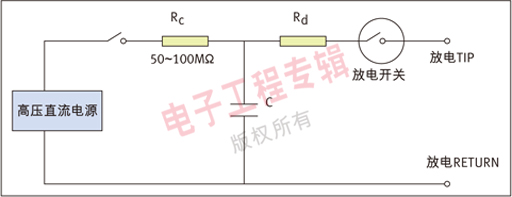

一款能够满足2kV HBM的芯片并不意味着它能够保证系统在IEC 61000-4-2标准规定的2kV放电条件下是安全的。图1是通用的ESD人体模型。

图1:ESD人体模型。

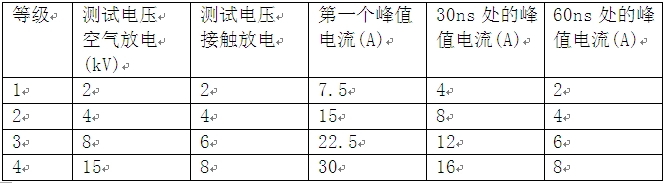

根据MIL-STD-883中的方法3015,在器件级,通过一个1.5kΩ电阻进行2kV的放电所导致的峰值电流大约为1.33A。但在系统级,IEC61000-4-2则被划分为4个威胁等级,即2kV、4kV、 6kV和8kV。与2kV威胁等级对应的峰值电流为7.5A。实际上,目前绝大多数系统都是按照等级4进行设计的,其峰值电流为30A(表1),该电流比芯片所能承受的电流大约高22倍。因此,为了实现更高系统级ESD防护,应该遵循系统级的HBM IEC 61000-4-2标准。

表1:IEC61000-4-2严重等级和测试电压。

{pagination}

钳位电压和响应时间

在2008年1月初,视频电子标准协会(VESA)颁布了Displayport标准的1.1a版,其中的第3.5.4节描述的就是ESD防护标准,它针对基于DisplayPort的系统和器件分别规定了不同的ESD要求。根据标准,基于DisplayPort的系统必须保护所有可能外露的接口信号和电源引脚能够满足或超过IEC 61000-4-2等级4(8kV接触放电)中的EOS(电过应力)指标而不会损坏。与Displayport器件(发送器IC、接收器IC和相关的I/O电路)相关的所有信号和电源引脚都必须至少能够承受JEDEC JESD22-A114-B Class 2(2kV 人体模型,200V机器模型)的静电冲击。

IEC61000-4-2

符合IEC61000-4-2额定值的器件并不一定能够保证系统可以通过ESD测试。保护器件的目的是将8kV IEC 61000-4-2接触式输入电压降低到受保护IC能够承受的安全电压范围。根据定义,钳位电压指的是ESD发生期间保护器件上的最大电压降,也是受保护IC上所见到的应力电压。理想的保护器件在正常工作中应该是察觉不到的,在遭受ESD冲击时应能立即导通,并将保护器件上的电压限制在稍高于正常工作电压之上的一个值,而且要远低于破坏门限。这在DisplayPort应用中极为重要,因为Displayport器件的I/O线的单端波动幅度要求限制在±0.3V内,而共模偏置参考电平最大值为2V。

如今业界的通常做法是公布器件的钳位电压,该电压的依据是上升时间和持续时间分别为8uS和20uS的脉冲。大多数数据手册会利用一个电流为1A甚至是更高的脉冲来表征他们的钳位电压。有时候,还会提供一张钳位电压和峰值电流的关系图。钳位电压确实是用于比较器件钳位性能的一个非常好的数据,然而它与IEC61000-4-2中定义的非常快的ESD脉冲却毫无关系。遭受ESD脉冲输入作用的器件上的电压波形截图能够很好地解释器件的钳位特性。钳位电压越低,受保护IC上的电压就越低,系统也就越能经受住ESD的冲击。

当比较两个器件的钳位性能时,比较的器件必须是用于同等的应用,具有相似的封装尺寸、电容范围和工作电压。当器件的数据速率连续增加到1Gbps甚至更高,对于DisplayPort来说是2.7Gbps时,ESD保护将面临更大的挑战。为了节省电路板面积,ESD保护器件的体积必须很小,同时为了不影响信号,电容和钳位电压也必须尽可能低。

响应时间和TVS二极管

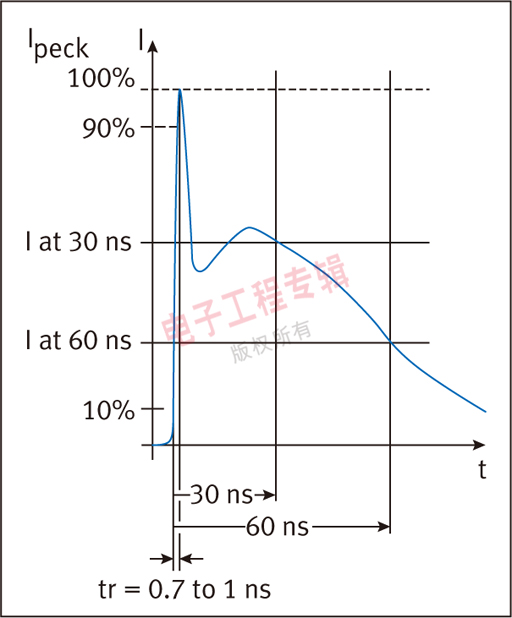

ESD是一个极快的瞬变脉冲。IEC 61000-4-2模型规定脉冲的上升时间为700ps到1ns, 持续时间为60ns(图2)。

图2:符合IEC 61000-4-2规范的ESD波形。

这意味着保护电路需要极快地导通来响应IEC61000-4-2脉冲才能保护系统,因此在选择ESD保护器件时,响应时间是一个重要的考虑参数。

首选的ESD保护解决方案是利用TVS(瞬变电压抑制器)二极管。TVS二极管是采用特殊技术的一种二极管。

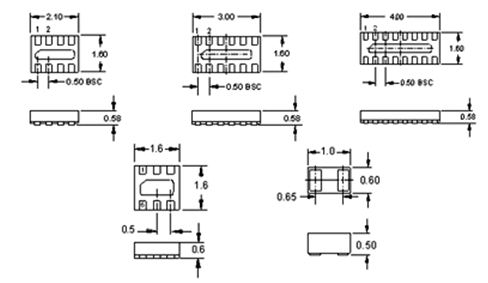

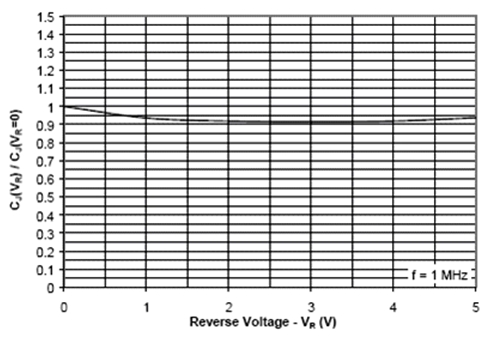

这种二极管体积很小(图3所示是Semtech公司的符合RoHS要求的SLP封装二极管),电容很小(图4所示的线间电容典型值仅0.3pF),泄漏电流也很小,对ESD冲击的响应时间非常快。最重要的是,它具有很低的钳位电压,并且在重复浪涌冲击后性能不会降低。

图3:Semtech公司符合RoHS要求的SLP封装(不是最终的)。

图4:标称电容与反向电压的关系(RClamp0524P)。

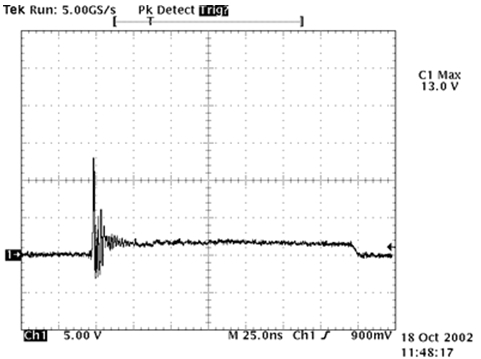

TVS二极管对IEC61000-4-2标准中定义的+8kV接触放电事件的典型ESD响应曲线如图5所示。TVS可以在几纳秒时间内将8kV的高压钳位到13V,从而有效地保证了受保护IC的安全。

图5:TVS二极管对IEC 61000-4-2中规定的+8kV接触放电事件的ESD响应。

{pagination}

信号完整性和CTS

为了确保DisplayPort产品之间的互操作性,所有设备必须满足Displayport一致性测试规范中制定的各项要求。

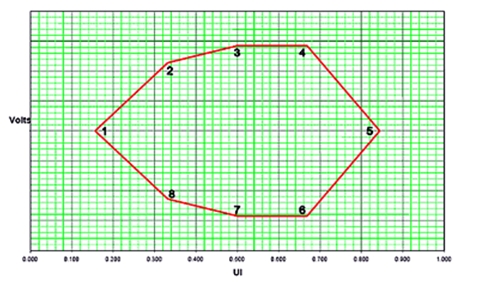

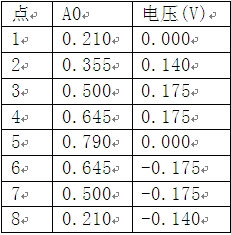

在Displayport应用中,高速音视频数据通过四个差分数据对来传送。没有专门的时钟信号对,时钟是通过8B/10B编码嵌入在数据流中。Displayport CTS要求发送器满足图6中的眼图模板要求。

图6:源连接器引脚处的眼图模板(摘自DisplayPort标准 V1.1a)。

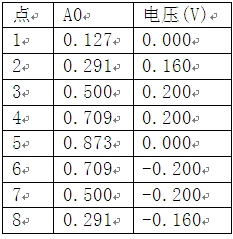

表2显示了2.7Gbps比特率的高点值,表3显示了比特率下降到1.62Gbps时的高点值。

表2:高比特率 (2.7Gbps) 时的模板高点。

表3:低比特率(1.62Gbps)时的模板高点。

阻抗和CTS

保护器件可能会从电气和机械两方面影响高速信号。由于阻抗的变化或平衡差分对的失配,这些影响将是不连续的,很容易导致信号质量变差。

DisplayPort CTS要求电缆和连接器符合严格的阻抗指标-夹具、连接器和走线管理的阻抗为100Ω±10%,电缆的阻抗为100Ω±5%。阻抗指标必须采用阻抗受控的夹具和时域反射仪(TDR)进行测试。夹具的上升时间必须为50ps(20%-80%)或更高,而测量数据的读取必须过滤到tr=130ps(20%-80%)。

器件的非理想特性将在高速差分对上产生额外的电感和电容负载。随着上升时间的变快,这些阻抗失配将会对差分阻抗产生更严重的影响,从而导致信号质量的劣化而无法通过眼图测试。因此即使上述阻抗要求对于源设备和接收设备来说不是强制性的,但还是推荐遵守。

容性负载

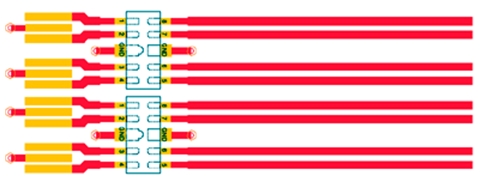

ESD保护器件的容性负载会引起有害的差分阻抗值的起伏变化,并导致TDR测量不能通过。有时候,可以通过采用合理的PCB版图设计来补偿由于有效的ESD保护器件所引入的容性负载。Semtech公司的RClamp0524P作为业界第一个ESD解决方案,提供超越IEC 61000-4-2等级4的ESD可靠保护,并且不需要上述的电容补偿。其I/O引脚间的电容典型值为0.3pF,对高速信号线上的电气影响非常小,因此该器件可以用到工作频率超过3GHz的电路中而不会对信号造成有害的影响。从机械学的观点看,RClamp0524P采用了专门能减小对高速信号影响的SLP2510P8封装,其特殊的流通型设计(见图7)允许印制导线直接穿过器件,可以尽量减少设计师对版图的修改。

图7:Semtech公司RClamp0524P的流通版图。

体积小、超低电容和高等级的ESD保护这三者的独特组合使得RClamp0524P能够成为工作频率高达2.7Gbps的Displayport设备的优秀解决方案。

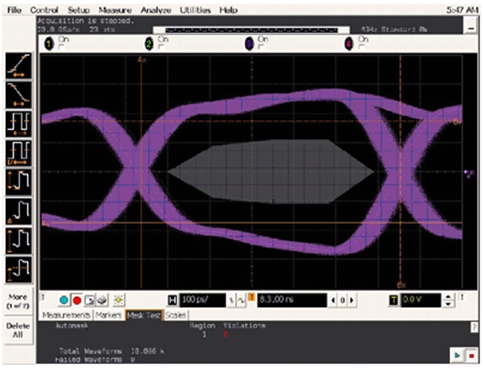

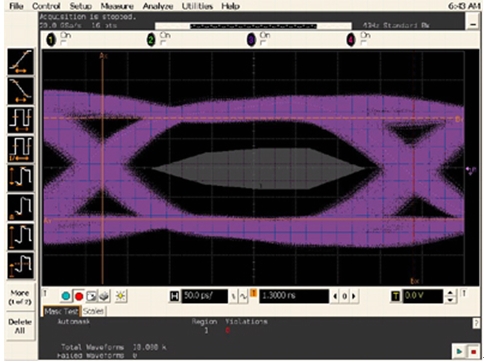

图8和图9是对受RClamp0524P保护的分别工作在2.7Gbps和1.62Gbps的Displayport的眼图测量结果。很明显,两种情况下眼图测试都合格。

图8:DisplayPort眼图测试结果(受工作在1.62Gbps的RClamp0524P的保护)。

图9:DisplayPort眼图测试结果(受工作在2.7Gbps的RClamp0524P的保护)。

{pagination}

Displayport介绍

2005年5月,视频电子标准协会(VESA)宣布开发新型的数字接口规范-Displayport。支持该规范的公司包括戴尔、惠普、Genesis Microchip、三星、恩智浦、 Intel、AMD/ATI、NVIDIA、Molex以及泰科。2006年5月,VESA宣布批准了DisplayPort 1.0;2007年3月发布了DisplayPort 1.1;2008年1月11日,1.1a版公开发行。

DisplayPort标准定义了一个开放的数字通信接口,可用于像PC或监视器内部接口这样的内部连接,也可以用于外部的显示器连接,包括PC和显示器或投影仪之间、PC和电视机之间或者是像DVD播放器和电视机显示器这类设备间的接口。

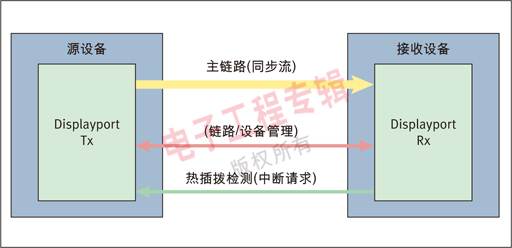

DisplayPort链路由一个单向主链路、一个双向的辅助链路和一个热插拔检测信号链路组成(见图10)。每个主链路包括1个、2个或4个交流耦合、双重端接的差分对(通道),但没有专门的时钟信号,时钟信号被嵌入在8B/10B编码的数据流中。交流耦合使得Displayport发送器和接收器可以用不同的工艺制造,因而可以在不同的共模电压条件下工作。

图10:Displayport数据传输通道。

DisplayPort支持两种链路速率,即2.7Gbps 和1.62Gbps。链路速率与像素率是没关系的,而通道数量与像素比特深度和分量比特深度之间也是独立的,这意味着可以很容易地在像素深度、分辨率、帧率以及像音频和HDCP(高带宽数字内容保护)这类附加信息数量之间进行折中权衡。

例如在四个通道上可以实现一个96帧/秒、1920x1080像素逐行扫描方式的12比特/像素、4:4:4 YCrCb视频流,或者60帧/秒、2560x1536像素的10bit RGB视频流。独立双向辅助通道的带宽为1Mbps,最大延迟为500ms,可以用于链路管理和设备控制。

产品营销工程师

Semtech公司