系统公司需要更高的生产能力,同时减少开发高级PCB系统的成本与时间,而这促使IC公司开发高级SERDES IO架构。这些SERDES IO架构包括前馈均衡器、判决反馈均衡器和时钟及数据恢复电路,使用当前的建模标准对它们进行建模非常困难甚至不可能。此外,通过这些新架构,对信号质量(开眼与闭眼)的观察从封装引脚转移到IC内部,并且是从信号中重新获得时钟与数据之后。这也对测量设备供应商带来了挑战。

在PCB上,SERDES设备驱动被视为串行链路的差分对。更高的带宽和吞吐量需要对系统级的串行链路提出了非常高的可靠性要求。某些标准要求在此类串行链路上传输10到12比特出现的错误不超过1位。为确保板级串行链路设计,系统公司必须模拟带有SERDES收发器模型的串行链路,或者制作该系统的功能完备的实体原型。比起制作实体原型,模拟的方式才是首选,这样可以降低成本和缩短设计周期时间。

为执行这些模拟,系统公司需要从IC公司获得可以在市面上提供的PCB模拟环境中使用的模型。模拟环境应该能够在可接受的时间范围内预测具有极长数据流(超过一千万比特)的串行链路的行为。

由于当前的IO建模标准过于依赖设备/电路级建模技术,IC设计公司本身在过去3到4年时间里开发了他们自己的内部SERDES IP建模和串行链路模拟环境,用于对他们的设备进行验证和关联。由于缺乏能够消化这些模型的工具,IC设计公司被迫将他们内部开发的工具发布给系统公司客户,让他们模拟自己的SERDES IP。如果系统公司能够在串行链路的两端都使用他们的IP,IC设计公司自然会很欢迎。但是,很有可能在串行链路的另一端,使用的是来自不同IC公司的IP,从而为系统设计公司带来互用性问题。与此同时,IC公司不想进入EDA领域——开发、发布和支持PCB模拟工具。

IC可能会希望能有一种业界标准建模技术,让他们可以对他们的高级SERDES IP的行为进行建模的同时,在将模型发布给系统公司客户的时候保护他们的IP。这样就需要一种新的方法解决高级SERDES IP公司的建模需要。为了开发这种技术,人们已经投入了大量的努力。SERDES IP公司对于新技术的主要要求包括以下几点:

* 能够对复杂的DSP类行为进行建模,例如滤镜优化、判决反馈均衡、时钟与数据恢复。

* 保持模拟时间最小化的同时实现高度的精确性(硬件关联)。

* 保护SERDES IP。

* 能够在晶片开发前对IP进行建模和评估。

* 作为一种公共标准被EDA供应商支持(这可以解决互用性问题)。

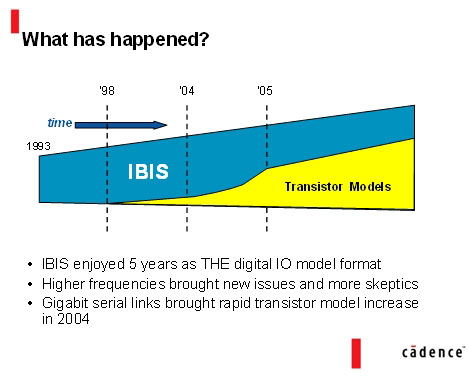

图1:吉比特串行链路使晶体管模型从2004年开始迅速发展。

有人提议将IBIS(BIRD 104)进行强化让IP供应商设计可执行的算法模型,插入到PCB模拟环境中。该提议在很多方面都是非常独特的。首先,它获得了多家EDA公司的支持,是与领先的SERDES IP供应商合作开发的;其次,EDA供应商和IP供应商开发了软件和模型,在该提议被采纳和修改IBIS之前就已经证明了此概念的可行性。其三,算法建模界面(AMI)工具包已经推出,并通过IBIS网站发布。目前为止,IBIS与固定IO模型(‘B’驱动器)配合,插入到EDA供应商的PCB模拟器中,而IC公司提供参数描述他们的IO驱动器和接收器。换句话说,只有一个模型被用于描述IO缓冲器的行为。这种方法在2003~2005年都是非常管用的。但对于高级SERDES IO架构,还提出了以下需求:

a)使用“黑盒子”模型技术将模型行为定义从EDA供应商工具内部转移到IO缓冲器模型内部;

b)定义“黑盒子”模型与EDA平台之间的交互作用。

通过该提议,IBIS进入到了全新的时代——具有可执行的模型,其行为在IO模型内部进行模拟,而不是在EDA平台内部。这就为IP供应商对新架构进行建模提供了高得多的灵活性,不用等待IBIS的修改。BIRD104是朝此方向迈出的第一步,并将被改进以应对类型更多样的架构和行为。不过通过“黑盒子”技术能够比之前的方法处理更多的SERDES架构。这是一种思维的转换,是IBIS的一个方向性的变化。

该提案最初是由Cadence与IBM紧密合作开发的,能够让IP供应商对高级SERDES设备进行建模,不论其使用何种语言。它让IP供应商创建黑盒子模型,通过一个非常简单而强大的基于C语言的API与EDA平台进行交互。由于黑盒子模型被作为共享文件或动态链接库(DLL)提供给系统公司,这种新技术可以对内容进行充分的模糊化处理,满足SERDES供应商保护其IP的需要。由于可以在算法层面上对高级SERDES设备进行建模,该模型可以极其迅速地让EDA平台满足系统公司用户的需要,在非常短的时间内模拟超大流量的数据流。

当BIRD104获得EDA公司和SERDES IP开发商的采用和支持,就可以实现模型的互用性。使用算法对高级SERDES行为进行建模的能力让IP供应商和系统公司可以在PCB设计环境中,在制作硅片之前对IP和目标串行链接进行探查和验证

为实施BER测试并输出“浴盆(bathtub)曲线”,测量工具必须对接收器(或者至少是CDR电路)进行模拟。测量工具必须假定RX模型能够执行这些测试。通过算法模型,该工具拥有了接收器的真正模型,移除了方程式中的所有假设。算法模型从而使得将相同的软件带到测量平台以及EDA平台上成为可能。这是两个平台之间空前紧密的联系,实现了模拟与测量之间更好的关联。

自从Cadence和IBM在2006年6月首次提交让IBIS可以支持可执行算法模型(通过AMI-API)的提案以来,在15个月的时间里,IBIS高级技术建模小组委员会成员一直在勤勤恳恳地工作。此后他们又进行了大量艰苦的工作,做出一份正式的提案,进一步拓展IBIS,该提案最近于2007年10月10日提交。Cadence已经开发并发布了“算法模型开发套件”,帮助IP供应商学习这种新技术,并开发和发布可以对应PCB模拟环境的算法模型。最近,该工具包的一个更新版刚刚通过IBIS网站发布,它被用于进行算法模型可互用性的“概念校验”测试。用户可以下载包含模型代码样本的工具包,这是一个可执行的基本测试器,能够测试模型和基本文件。

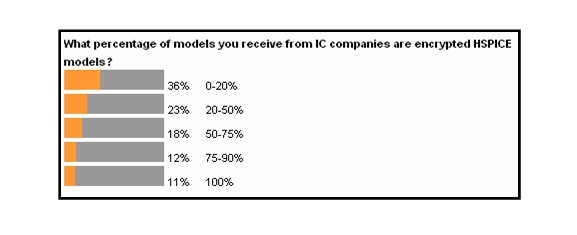

图2:调查结果有64% 的人表示20%以上的模型是以Hspice加密的。

算法建模方法学为模型开发者带来了极高的性能和灵活性,使他们能够对设备进行精确建模,并满足他们所需的所有的IP保护性能。它带来了革命性的变化,使得复杂的多吉比特级收发器可以被建模用于高速IO电路。通过多家EDA供应商和IP公司的支持,该技术在无需制作实体原型的情况下,将给系统设计公司带来其迫切需要的互用性,以及为预测BER所需的超大码流的仿真能力。

作者:Hemant Shah

产品营销部主管

Cadence公司