随着液晶面板的兴起以及越来越大的尺寸,高压LCD驱动日渐受到市场的关注,但高电压(40V以上)工艺在中国基本还处于空白。本文着重介绍40V高压工艺平台所面临的主要问题和关键工艺:锑注入,外延生长之后的光刻对准和非金属硅化物接触孔等。此外,由于成本的控制以及保证相当的市场竞争力,该套工艺开发的掩模版层数相当少,只有16层,这就给器件的调整带来了极大的复杂度和难度,往往“牵一发而动全身”,一次器件的调整往往同时影响好几种器件,顾此失彼。而且还要面临良率的问题,我们的目标是要将良率做到90%以上。基于以上考虑,我们将主要精力集中在这些关键工艺的开发和器件的调整,最终通过所有的验证,并达到了99%的良率。下文将通过实验过程及相关数据进行详细说明。

锑注入

在保证器件能正常工作且有一定的工艺窗口的情况下,选择锑注入的能量和剂量以及相应的推阱工艺并满足以下要求:

1. 在外延生长完没有位错/层错缺陷;

2. 明确氧化层厚度与锑注入的能量/剂量以及相应的推阱工艺之间的关系;

3. 氧化层厚度在锑注入区与非注入区的不同。

由表1可见,在有衬垫氧化层的情况下,低的锑注入能量/剂量是没有缺陷的条件并且随着锑注入的能量/剂量越来越高,位错/层错缺陷越来越严重(见图1)。在氧化层厚度与锑注入能量/剂量以及注入/非注入区的关系方面,我们做了相关研究(见表2)。我们注意到,在相同的推阱条件下越接近表面的越严重的硅损伤将会得到更厚的氧化层。这也意味着,在后续的氧化层去除工序时我们要充分考虑这一点。另外一点需要提到的是,为了避免锑和磷的交叉污染,我们这里所采取的措施是指定一台机台专门负责锑的推阱工艺。

硅外延生长后的光刻对准和OVL

由于在外延生长完后,我们接下来要进行的就是N/P阱光刻,而这2次光刻所对准的前层都是外延生长前的零层。但经过外延生长的零层图案是否还保型完好到足以让我们的光刻机轻松识别呢?答案是否定的!由于我们的外延比较厚以及外延工艺本身的特性,前层的图案在外延生长过程中或多或少会产生一些形变或位移,这就给后续的光刻对准带来了困难。

表一:不同能量、剂量的锑注入与缺陷的关系

表二 氧化层厚度与锑注入能量/剂量以及注入/非注入区的关系。

图一:不同锑注入能量/剂量下的缺陷光学比较

为了解决以上问题,保证光刻机能正常的对准以及相当精确的OVL,我们同光刻部门就LSA/FIA 对准图案的选择进行了大量的实验并且得到了不错的结果:

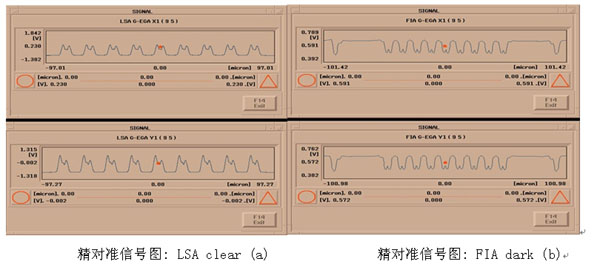

首先考虑粗对准。比较图2(a)和(b),明显我们看到LSA dark图(b)的粗对准信号图更好,更容易让光刻机粗对准。接下来考虑精对准。比较图3(a)和(b),明显我们看到FIA dark图(b)的精对准信号更好,更容易让光刻机精对准。

图二:光刻机不同粗对准图案的信号图

图三:光刻机不同精对准图案的信号图

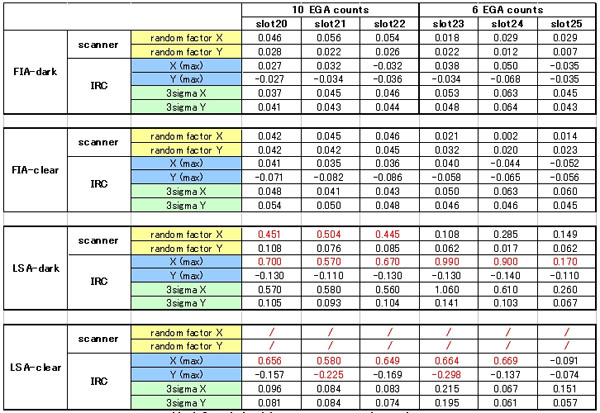

在确认了光刻机的粗对准和精对准信号之后,我们还需要进一步确认光刻机相应的精对准随机因子和Overlay的结果。从表3看出,LSA不管clear还是dark,其随机因子和OVL结果都相当差;而FIA则不管是clear还是dark,其随机因子和OVL结果都相当好。另外,至于Global EGA到底是否可以少选几个点而进一步改善,从数据上看似乎没有太大区别。

表三:不同精对准图案与随机因子/Overlay的关系

非金属硅化物接触孔

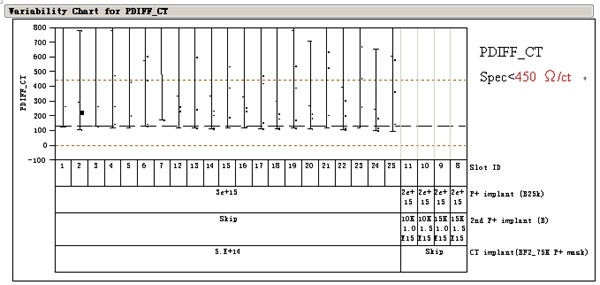

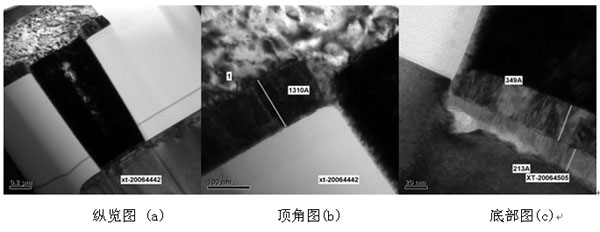

由于采用非金属硅化物接触孔,虽然理论上相比金属硅化物接触电阻会偏大,但由于我们是第一次采用这种工艺,并没有基准可以参考,结果发现我们的工艺PDIFF_CT指标大大超出了规格(见图4)。

图四:非金属硅化物PDIFF_CT WAT值

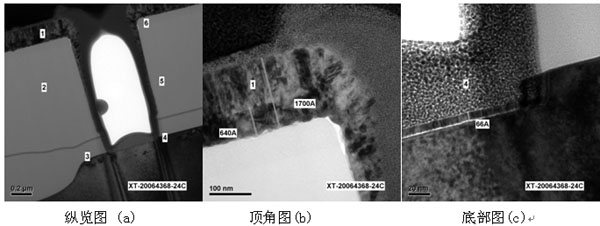

经过TEM FA我们发现,Ti/TiN在接触孔底部的阶梯覆盖相当的差(图5)。当我们采用金属硅化物工艺时,由于接触孔底部已经有一层TiSi2,这种影响并不太大。但是,一旦采用的是非金属硅化物接触孔,如此差的底部阶梯覆盖就是致命的。

图五:接触孔Ti/TiN阶梯覆盖图

知道失效原因之后,经过详细讨论和仔细研究,我们调整了Ti/TiN金属淀积和接触孔刻蚀的工艺从而得到了图6的形貌。可以看到接触孔底部的阶梯覆盖得到明显的改善,这一形貌的改善在WAT PDIFF_CT的数据上我们得到了验证(图7)。经过工艺的改善,PDIFF_CT从之前大于450降到了100以下,并且硅片面内均匀性相当好。

图六:改善后接触孔Ti/TiN阶梯覆盖图

图七:新结构接触孔PDIFF_CT WAT值

器件的调整

在以上的新工艺开发基本解决之后,接下来我们的重点就是器件的调整。由于40V高压所用的掩模版非常少,一道离子注入层往往同时影响好几个器件或者说一种器件的调整往往取决于好几道离子注入。这虽然使得我们的工作变得更加复杂,但却还不是最棘手的问题。我们面临的最大问题是如何尽可能同时提高40V高压器件的击穿电压(BV)和工作电流(Ion)。众所周知,这两个参数往往是相互影响、相互牵制的。

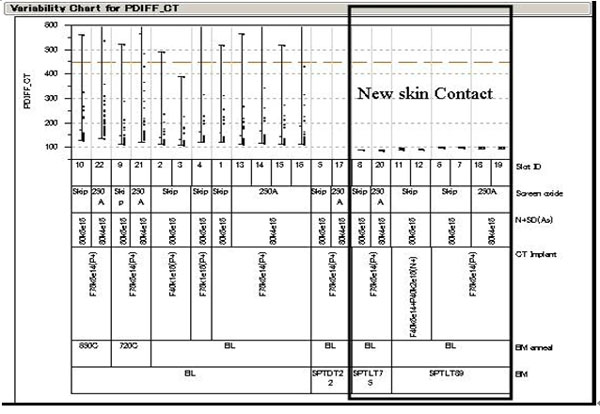

图八:40V高压PMOS 器件结构图

那么我们要怎样做才能实现呢?让我们先了解一下40V高压器件的器件结构。如图8所示,我们40V高压器件采用的是LDMOS结构,源极/漏极的OFFSET由阱构成。在栅极多晶硅和源极/漏极之间有一段漂移区 氧化层。就PMOS而言,整个PMOS被NBL(N-Buried Layer)和N阱隔开。为了提高BV,我们首先得知道,器件的BV取决于源极/漏极穿通(Punch Through)还是某一个PN 结。事实上,当我们做过大量的实验之后发现,40V PMOS BV取决于漏极的P阱对NBL结的BV,因此,我们的目标就是如何提高这个结的BV。为了实现这个目标,我们可以有两种做法:

1. 降低NBL和P阱浓度。但这里要注意,如果P阱浓度太低,由于Rs增加和结深变浅会相应减小Ion。另一方面,如果NBL浓度太低,则有可能导致中间的N阱同NBL接不上,从而导致HVPMOS完全不工作。

2. 增加外延层(EPI)厚度。外延增厚不仅可以明显提高HVPMOS BV而且由于结深的增加,Ion也能得到相应的增加。虽然外延变厚同样有可能导致中间的N阱同NBL接不上,但只要我们控制在一定范围内,这个问题就能得到避免。

比较以上两种方法,由于后者对提高BV更有效,而且同时还能提高Ion,因此我们选择增加外延厚度。不过这里要再次提醒,外延不能太厚,否则HVPMOS将完全不能工作。虽然我们通过增加外延厚度间接提高了Ion,但是离我们的目标还有一定的距离。因此,我们还得从另一个角度来进一步提升。

注意到在栅极多晶硅和源极/漏极之间有一段漂移氧化层,如果我们能降低漂移氧化层下面的P阱 Rs则又能进一步提升Ion。顺着这条思路,我们可以在场 氧化层成长以前增加一次硼(Boron)注入来降低Rs。事实上,我们正是这样做的,并且确实进一步提升了40V PMOS Ion。不过这里同样要注意两点:

1. 这次硼注入增加了P阱的浓度,因此这有可能降低HVPMOS的BV,需要权衡考虑;

2. 这次硼注入同样会注入到N阱区域,因此这将增加N阱的Rs,从而降低40V NMOS Ion,也需要权衡考虑。

良率的提升

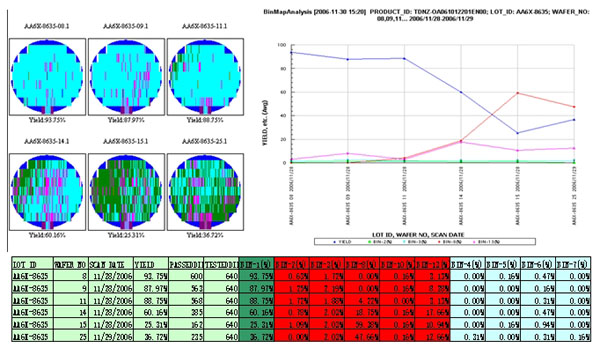

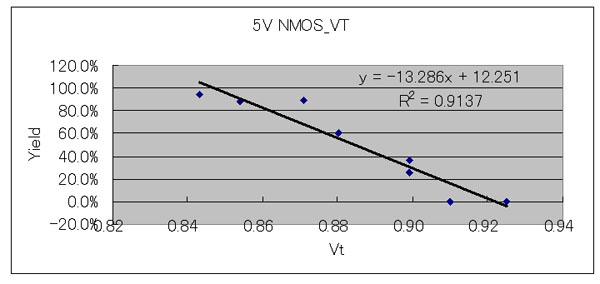

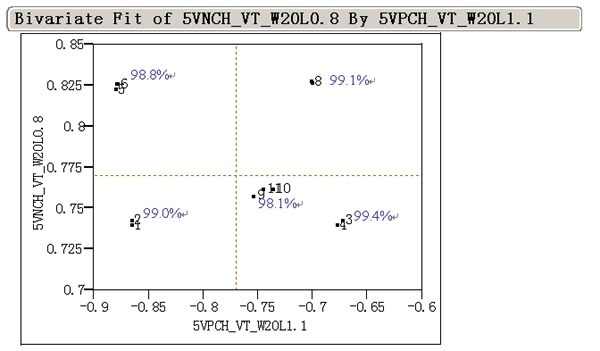

在工艺和器件的问题基本解决之后,我们进一步要做的就是确认我们的良率大概是多少以及应该怎样提升。先来看基准良率。从图9的良率bin map我们可以看到,良率从25%到94%不等,并且主要是Bin8和Bin13失效。另外,我们总结了良率与WAT的关系,发现良率与5VNMOS Vt有着很强的联系。由图10可见,随着5VNMOS Vt的升高,良率越来越低。基于以上分析,我们迅速调整了5VNMOS Vt,结果良率提升到了99%(图11)。

图九:40V高压良率及bin map

图十:5VNMOS_Vt 与良率的负相关系

图十一:5VNMOS Vt调整后良率与Vt的关系

本文小结

从以上的数据可以看出,该40V高压工艺平台的开发相当成功,这不仅反映在各项监控指标和最终的WAT上,而且高达99%的良率更是肯定了这一点。因此,40V高压工艺的开发成功不仅填补了中国在该技术上的空白,完善了高压产品系列,而且还将带来显著的经济效益。另外,这些关键工艺不仅适用于40V高压,未来其他的项目也可以借鉴。

高级主管工程师

熊涛

资深工程师

工艺集成技术开发部

华虹NEC电子有限公司