能够利用仿真和原型设计以及基于小芯片的连通性 PHY IP 进行硬件和软件的共同验证和全系统的功耗分析,以实现对延迟、带宽和功耗进行功耗、性能和面积 (PPA)的优化。

提供定制模拟设计和电路板设计、集成电路 (IC) 寄生参数提取、静态时序分析 (STA) 签核,信号和电源完整性 (SI/PI)、电磁干扰 (EMI) 以及热分析的协同设计能力。

如需获取完整版PPT资料, 请点击“PPT申请” 按钮;注册成功且通过Cadence审核的用户可获得完整版PPT资料。

注:

审核通过后Cadence会将PPT发送至您的邮箱,提供您的公司邮箱地址通过审核的几率更大哦!

流程管理与物理实现

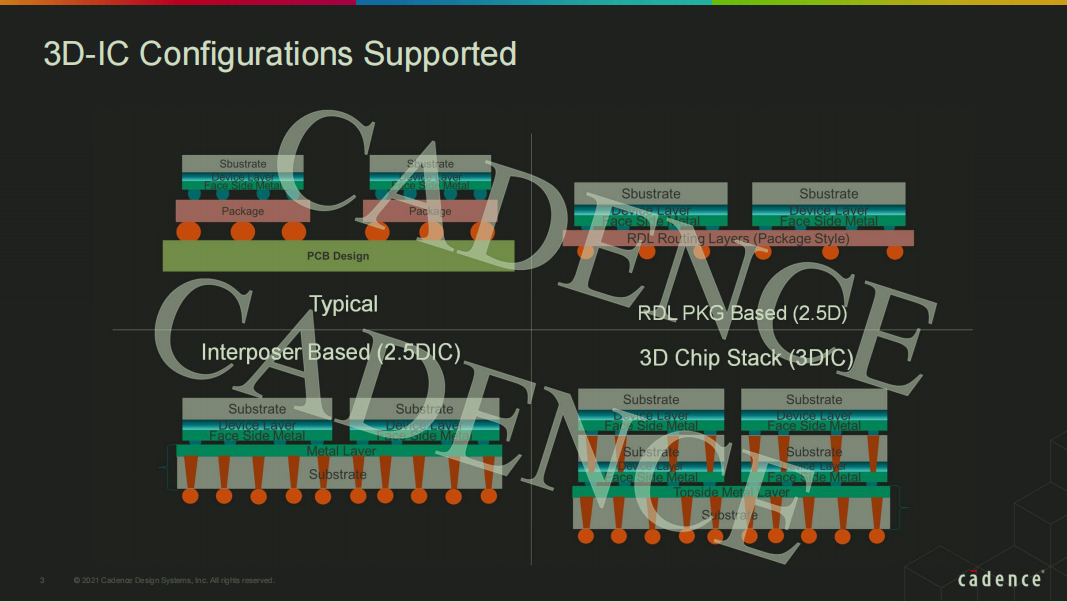

Integrity 3D-IC可以根据系统类型和团队组织架构提供不同设计流程,赋能设计团队以快速、高效、强大的三维系统设计能力。

-

PPT申请

PPT申请3D System Planning

3D系统顶层设计,综合考虑热、供电、 时序实现最佳晶粒堆叠Bump定义

Integrity 3D-IC设计成败首先取决于系统规划。基于点工具的传统手动流程也可以设计3D-IC,但周期长冗余度高难以进行早期探索迭代。 Integrity 3D-IC赋予设计者极大的设计自由度,高效应对晶粒堆叠拓扑、Bump规划,TSV布局等设计挑战,辅以业界领先的Cadence系统分析平台实现最佳系统PPA。

-

PPT申请

PPT申请HBM Interposer Routing

可全自动可自定义配置模式的最优中介层绕线

3D-IC目前常见的实现是基于中介层的HBM-CPU/SOC设计 ,Integrity 3D-IC将以日和周为单位的手动绕线加速到秒级和分钟级,轻松满足性能、信号电源完整性与设计迭代的多重要求,为高带宽高数据吞吐量的机器学习、超算、高性能移动设备、端计算等应用提供最佳设计支持。

-

PPT申请

PPT申请Top-Down 3D Partition Flow

全新自顶向下3D系统切分设计

从设计初始就充分考虑三维实现的自由度能提供最佳系统性能。Integrity 3D-IC助力架构和布图规划设计师从全局考虑不同模块在三维空间多层级上的逻辑物理分布。通过Cadence强大的的层次化早期布图规划算法实现不同单元、模块、IP在不同层次晶粒的最优分配,将3D-IC优势发挥到极致。

-

PPT申请

PPT申请Memory-on-Logic 3D-IC Implementation

3D近存计算的设计与物理实现

存算一体和近存计算是解决CPU/GPU/NPU总线和大规模片上网络拥塞的有效手段。通过Integrity 3D-IC特有的内存单元逻辑单元三维布局优化,芯片设计师可以更容易的实现高性能高带宽的系统设计,从而或者缩小原有系统封装面积或者进一步提高原有系统PPA。

-

PPT申请

PPT申请Bottom-Up 3D-Chiplet Integration

完美使用已有晶粒集成实现3D系统

通过自有或第三方晶粒搭建是实现新3D系统设计的最快方式。Integrity 3D-IC兼容已有晶粒设计,分析设计优化晶粒堆叠、Bump规划及连接关系,在数字模拟等各种芯片设计工具与系统规划平台之间轻松切换,以全系统视角和分析优化能力赋能设计团队高效完成单颗晶粒向三维全系统的组建。

3D性能分析与设计签核

Integrity 3D-IC强大的流程管理器可以灵活调用各种性能分析与签核工具进行早期分析迭代或后期签核。

-

PPT申请

PPT申请3D-IC Extraction and STA Solution

3D-IC寄生参数提取与静态时序分析解决方案

传统系统封装设计只能针对晶粒做单独的寄生参数提取/静态时序分析。 而Integrity 3D-IC结合Quantus/ExtractIM/Tempus等工具可以进行晶粒内、晶粒间和封装的寄生参数提取进而实现全3DIC系统级静态时序分析,从而做相应的的优化和设计迭代,提高系统PPA。

-

PPT申请

PPT申请3D System-Level DRC/LVS with Pegasus Verification System

集成Pegasus验证工具进行3D系统级物理验证

传统DRC/LVS只能做分立的片上或封装DRC/LVS分析,且必须依赖芯片制造和封装厂商提供设计规则手册进行片间LVS检查。 Integrity 3D-IC通过开创性的自动分析功能结合Pegasus检查晶粒间连接,在系统和晶粒设计早期规避因连接性导致的系统故障,最终在设计完成时进行全系统DRC和LVS签核。

3D多物理特性系统分析与签核

封装系统分析需要考虑多重物理特性,Integrity 3D-IC结合Cadence领先的MSA工具实现系统级的早期设计迭代和最终签核。

-

PPT申请

PPT申请SI/PI Analysis for 2.5D/3D System

2.5D/3D系统的信号完整性/电源完整性分析签核

2.5D和3D系统中的信号完整性和电源完整性验证对于3D封装设计的电性能尤为重要。一方面一些高速的数字信号如HBM总线、CCIX、UCIe等接口需要详细的信号完整性分析,确保接口之间具有足够的时许和眼图裕量。精细的三维全波电磁场分析是确保信号完整性分析精度的关键。另一方面,电源完整性的签核,需要兼顾各个逻辑或模拟芯片、硅载板、基板和PCB在不同频段区间对系统电源影响的比例,将各个子模块纳入同一仿真流程,并通过全面的时域或频域评估手段,将为系统电源的鲁棒性设计提供有力支撑。

-

PPT申请

PPT申请Voltus IC Power Integrity Solution's Power and Rail Analysis of 3D-IC

基于Voltus的三维系统功耗及供电分析签核

传统的针对单芯片进行电源完整性签核的方案无法分析芯片和芯片之间的耦合,会带来额外的设计风险或者冗余成本。 Voltus 3D-IC解决方案可用于业界所有2.5D/3D-IC的电源完整性分析,其高容量和高精度可用于分析高达数十亿门芯片的多芯片堆叠和100+ K端口的封装模型的电源完整性协同仿真, 能够实现3D-IC设计的快速迭代和收敛,降低设计冗余和芯片成本。

-

PPT申请

PPT申请Celsius Thermal Solver and Stress Analysis of 3D-IC

基于Celsius的三维热性能和热应力分析签核

三维堆叠芯片的设计方法, 可以提高系统的集成度、降低功耗、减少成本;但同时对于热量的传导, 温度的管理,以及热应力方面的可靠性提出了挑战。 结合Integrity 3D-IC平台,Celsius 提供精确快速的热性能、电性能和热应力分析,从早期的晶粒堆叠、Bump规划,TSV布局,到中期In-Design分析, 使得工程师能够及时修正芯片的缺陷,直至产品的签核 , 从而保证产品的PPA和缩短设计周期。

-

Cadence Integrity 3D-IC平台发布

-

Cadence Integrity_3D_IC

-

Design with Cadence- Lightelligence

-

Integrity 3D-IC介绍

活动时间:2022年5月11日-8月10日

奖品派发:活动结束1周后我们将联系您奖品邮寄事宜(活动最终解释权归Cadence所有)。

调查问卷

Cadence 拥有世界上最具创新精神的企业客户群,他们向超大规模计算、5G 通讯、汽车、移动、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续八年名列美国《财富》杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 cadence.com。